# <u>onsemí</u>

## Multi-purpose Three-Phase BLDC Predriver LV8968BBUW

#### Overview

The LV8968BB is a multi-purpose three-phase BLDC predriver for automotive applications and developed in compliance with ISO 26262. This 3-phase peripheral predriver offers a BEMF (Back ElectroMotive Force) output and the wide operating voltage range and AEC-Q100 qualification make this device ideal for automotive applications. Six gate drivers provide 400 mA (typ) gate current to external power bridges allowing use of low resistance power FETs as well as logic level FETs. All FETs are protected against overcurrent, short-circuit, overtemperature and gate undervoltage. A multitude of protection and monitoring features make this device suitable for applications with functional safety (FuSa) requirements. Three independent low-side source pins allow multiple shunt measurement.

The device also includes a programmable linear regulator, a fast current sense amplifier and a window watchdog for microcontroller support. The SPI interface allows for real time parameter setup and diagnostics. Critical system parameters can be programmed into nonvolatile OTP memory.

Junction temperature tolerance up to 175°C and control via wide level WAKE and PWM signals make the LV8968BB an ideal motor predriver for a wide range of ISO 26262 related actuators, fans and pumps.

#### Features

- Full Drive Power from 8 V to 28 V Supply Voltage with Transient Tolerance from 4.5 V to 40 V

- Extended Voltage Range from 6 V to 33 V Using Logic Level Mode

- Up to 30 kHz Motor PWM with Individual Six Gate Control or Drive-3 Mode with Integrated Programmable Dead Time

- 5 V / 3.3 V Linear Regulator for External Loads up to 50 mA

- Extensive System Protection Features Including:

- Drain-Source Short Detection for External FET

- Overcurrent Shutoff

- Low Gate Voltage Warning

- Overtemperature Warning and Shutoff

- Over / Undervoltage Protection

- SPI Interface for Parameter Setup and Diagnostic Access, Dynamic Access to Dead Time, Amplifier Gain, and Short–Circuit Levels

- Nonvolatile (OTP) Memory for Storing Critical System Parameters

- Wide Voltage Enable Line and PWM Interface

- Integrated Window Watchdog Timer Function

- AEC-Q100 Qualified and PPAP Capable

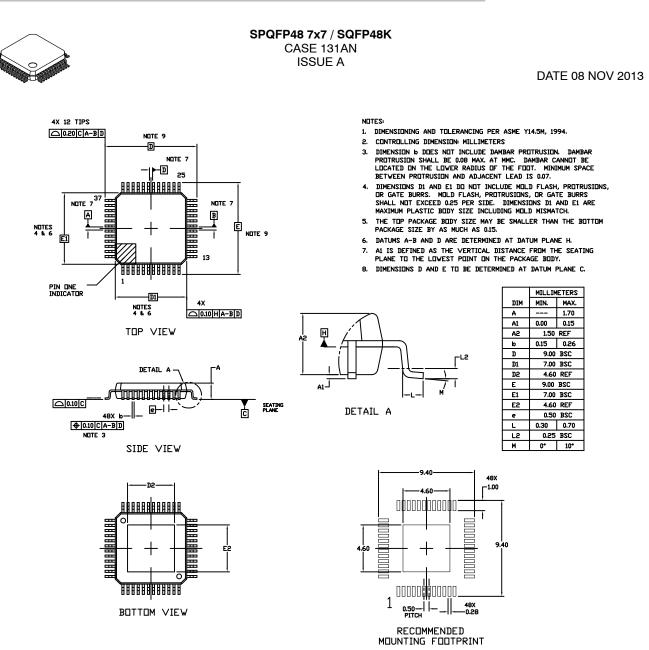

- Thermally Efficient Exposed Die 48 Pin SQFP Package for Transient Operation Up to 175°C

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

SPQFP48 CASE 131AN

#### **ORDERING INFORMATION**

|      | Device    | Package                                 | Shipping†             |

|------|-----------|-----------------------------------------|-----------------------|

| LV89 | 68BBUWR2G | SPQFP48K<br>(Pb–Free /<br>Halogen Free) | 2500 /<br>Tape & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### SAFETY DESIGN ASIL B

ASIL B Product developed in compliance with ISO 26262 for which a complete safety package is available.

#### **Typical Applications**

- Suspension, Park Brake, Transmission, Steering Pump, Vacuum Pump, Battery Pack Cooling, Sliding Door, Lift Gate etc.

- Robotics

- Light E-mobility and Motive Power

- Industrial Equipment

- White Goods

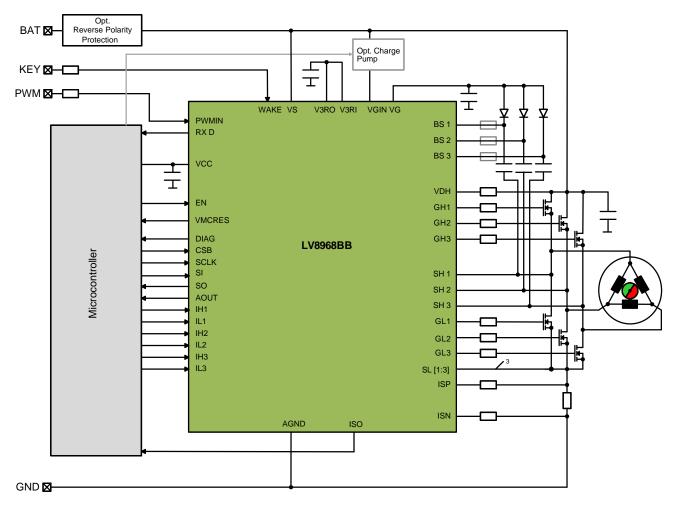

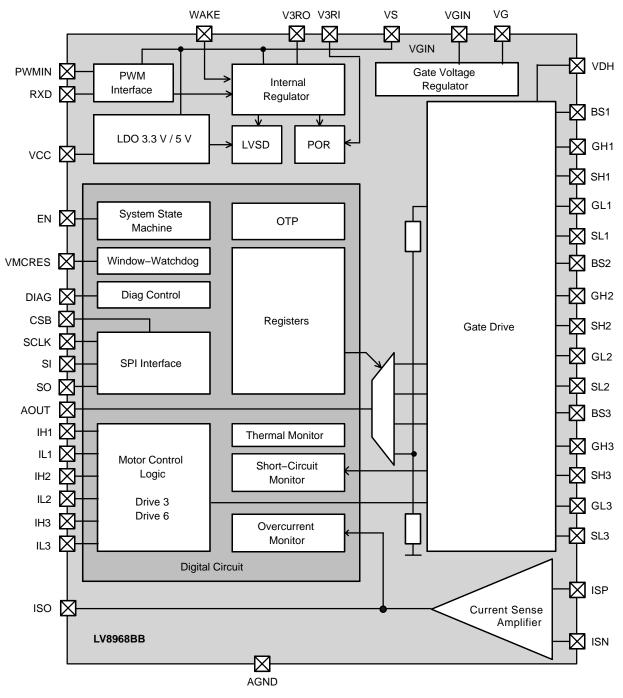

#### INTERNAL EQUIVALENT BLOCK DIAGRAM AND APPLICATION CIRCUIT

Figure 1. Typical Application Diagram

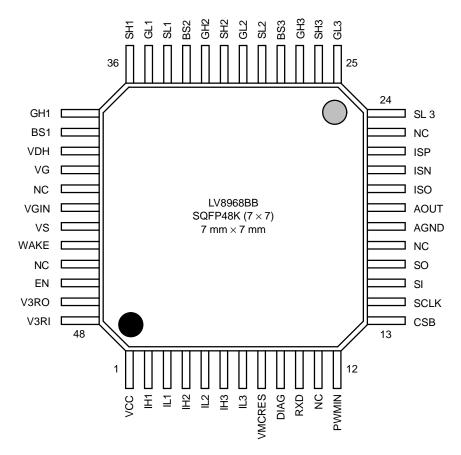

#### **PIN ASSIGNMENT**

Figure 2. LV8968BB Pinout

#### **Table 1. PIN ASSIGNMENTS & DESCRIPTION**

| Name   | No. | Description                                                                                                                                           |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC    | 1   | 5 V or 3.3 V linear regulator output. (Selected by SPI register setting)                                                                              |

| IH1    | 2   | Active high, digital control input to activate GH1.                                                                                                   |

| IL1    | 3   | Active low, digital control input to activate GL1.                                                                                                    |

| IH2    | 4   | Active high, digital control input to activate GH2.                                                                                                   |

| IL2    | 5   | Active low, digital control input to activate GL2.                                                                                                    |

| IH3    | 6   | Active high, digital control input to activate GH3.                                                                                                   |

| IL3    | 7   | Active low, digital control input to activate GL3.                                                                                                    |

| VMCRES | 8   | Open drain reset output for the microcontroller. Goes low for VCC undervoltage fault, optionally for watchdog reset and thermal shutdown.             |

| DIAG   | 9   | Open drain error or diagnostic output to be connected to microcontroller interrupt line. DIAG functionality is defined by internal register settings. |

| RXD    | 10  | Open drain PWM data output to microcontroller.                                                                                                        |

| NC     | 11  | No connection.                                                                                                                                        |

| PWMIN  | 12  | Input for battery level control signal. The digital level of PWMIN appears on RXD.                                                                    |

| CSB    | 13  | High voltage level translator. Digital level is active low, digital SPI interface chip selection pin.                                                 |

| SCLK   | 14  | SPI interface clock input pin. SI data is latched during the rising edge.                                                                             |

#### Table 1. PIN ASSIGNMENTS & DESCRIPTION (continued)

| Name | No. | Description                                                                                                                                                                                    |

|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SI   | 15  | SPI interface serial data input pin.                                                                                                                                                           |

| SO   | 16  | SPI interface serial data output pin. High level is pulled to VCC.                                                                                                                             |

| NC   | 17  | No connection.                                                                                                                                                                                 |

| AGND | 18  | Ground pin.                                                                                                                                                                                    |

| AOUT | 19  | Output for various internal analog signals. Actual signal is selected via SPI register.                                                                                                        |

| ISO  | 20  | Output pin for current sense amplifier. Connect to AD converter input of the microcontroller for current sensing. Gain, reference, and overcurrent threshold is programmable via SPI register. |

| ISN  | 21  | Current sense amp minus input pin. Connect this pin to the GND side of the shunt resistor with Kelvin leads.                                                                                   |

| ISP  | 22  | Current sense amp plus input pin. Connect this through to top side of shunt resistor with Kelvin leads.                                                                                        |

| NC   | 23  | No connection.                                                                                                                                                                                 |

| SL3  | 24  | Low-side source connection of the power stage. Return path for gate current of GL3. Connect to source of FET controlled by IL3 or to common source of the power stage.                         |

| GL3  | 25  | Gate driver output for low-side FETs. Switches voltage level between VG and SL3. Use at least 10 $\Omega$ gate resistors to protect against current spikes.                                    |

| SH3  | 26  | Connection for the motor phase terminal controlled by GH3 and GL3. Return path for high-side drivers and input for BEMF sensing.                                                               |

| GH3  | 27  | Gate driver output for high-side FETs. Switches voltage level between BS3 and SH3. Use at least 10 $\Omega$ gate resistors to protect against current spikes.                                  |

| BS3  | 28  | Supply pin for high-side driver GH3. Needs a bootstrap capacitor to SH3 and a diode in reverse connection to VG.                                                                               |

| SL2  | 29  | Low-side source connection of the power stage. Return path for gate current of GL2.<br>Connect to source of FET controlled by IL2 or to common source of the power stage.                      |

| GL2  | 30  | Gate driver output for low-side FETs. Switches voltage level between VG and SL2. Use at least 10 $\Omega$ gate resistors to protect against current spikes.                                    |

| SH2  | 31  | Connection for the motor phase terminal controlled by GH2 and GL2.<br>Return path for high–side drivers and input for BEMF sensing.                                                            |

| GH2  | 32  | Gate driver output for high-side FETs. Switches voltage level between BS2 and SH2. Use at least 10 $\Omega$ gate resistors to protect against current spikes.                                  |

| BS2  | 33  | Supply pin for high–side driver GH2. Needs a bootstrap capacitor to SH2 and a diode in reverse connection to VG.                                                                               |

| SL1  | 34  | Low-side source connection of the power stage. Return path for gate current of GL1. Connect to source of FET controlled by IL1 or to common source of the power stage.                         |

| GL1  | 35  | Gate driver output for low-side FETs. Switches voltage level between VG and SL1. Use at least 10 $\Omega$ gate resistors to protect against current spikes.                                    |

| SH1  | 36  | Connection for the motor phase terminal controlled by GH1 and GL1.<br>Return path for high–side drivers and input for BEMF sensing.                                                            |

| GH1  | 37  | Gate driver output for high-side FETs. Switches voltage level between BS1 and SH1. Use at least 10 $\Omega$ gate resistors to protect against current spikes.                                  |

| BS1  | 38  | Supply pin for high-side driver GH1. Needs a bootstrap capacitor to SH1 and a diode in reverse connection to VG.                                                                               |

| VDH  | 39  | Sense input for supply voltage and short–circuit detection of high–side power FETs. Connect through 100 $\Omega$ resistor to common drain of the power bridge.                                 |

| VG   | 40  | Power supply pin for low-side gate drive GL[1–3] directly and GH[1–3] through bootstrap circuit. Connect decoupling capacitor between VG and GND.                                              |

| NC   | 41  | No Connection.                                                                                                                                                                                 |

| VGIN | 42  | Gate supply input. Normally shorted to VS. Insert a charge pump circuit between VS and VGIN if low voltage operation is required.                                                              |

| VS   | 43  | Power supply pin.                                                                                                                                                                              |

| Name | No. | Description                                                                                                                                                                                                                       |

|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAKE | 44  | WAKE up pin for internal power supply. "H" => Operating mode, "L" or "Open" => Sleep mode.                                                                                                                                        |

| NC   | 45  | No connection.                                                                                                                                                                                                                    |

| EN   | 46  | Active high digital input. A high on EN will activate the outputs. EN can be used as a hold input to allow an external microcontroller to keep the IC operating even if WAKE is low. A falling edge on EN clears the error flags. |

| V3RO | 47  | Internal regulator output pin. Connect capacitor between this pin and GND.                                                                                                                                                        |

| V3RI | 48  | Internal regulator feedback pin (Control circuit and Logic power supply).<br>Connect to V3RO pin.                                                                                                                                 |

#### Table 1. PIN ASSIGNMENTS & DESCRIPTION (continued)

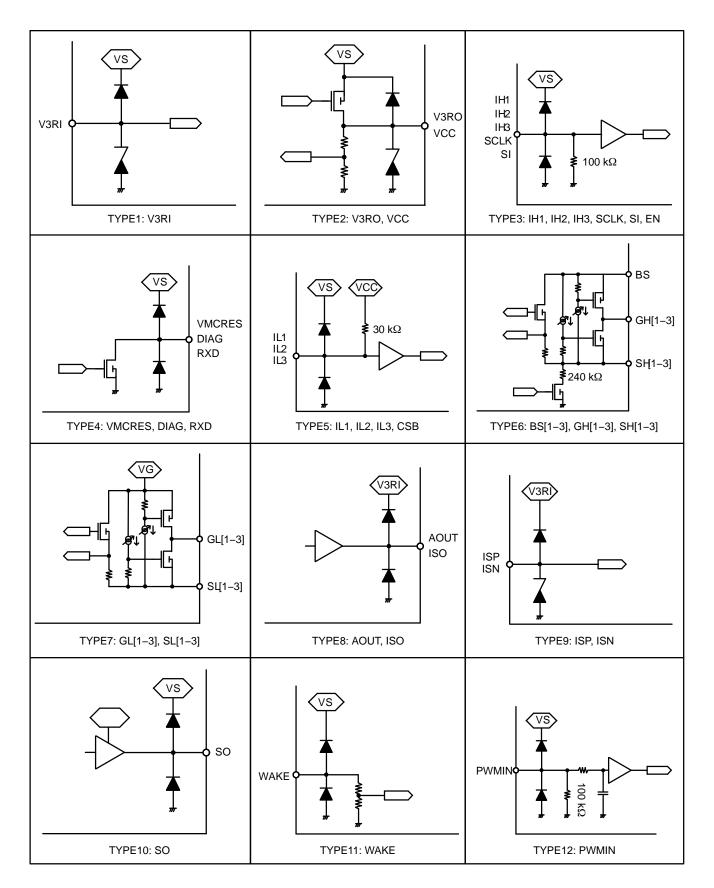

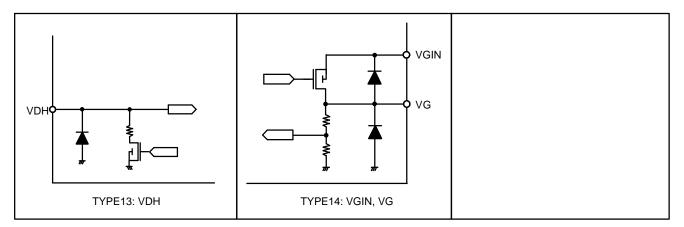

#### **PIN FUNCTIONALITY**

#### PIN FUNCTIONALITY (continued)

#### Figure 3. Pin Functionality

#### Table 2. ABSOLUTE MAXIMUM RATINGS

| Parameter                         | Pins                                | Ratings                        | Unit |

|-----------------------------------|-------------------------------------|--------------------------------|------|

| Supply Voltage                    | VS, VDH, VGIN                       | -0.3 to 40                     | V    |

| Gate Voltage to GND               | VG                                  | -0.3 to 40                     | V    |

| Bootstrap to GND                  | BS[1-3]                             | -0.3 to 40                     | V    |

| Bootstrap to SH[1-3]              | BS[1-3]                             | -0.3 to 40                     | V    |

| Logic Power Supply                | V3RI, V3RO                          | -0.3 to 3.6                    | V    |

| 3.3 V / 5 V Regulator Voltage     | VCC                                 | -0.3 to 5.5                    | V    |

| VS Level Signal Voltage           | WAKE, PWMIN                         | -0.3 to 40                     | V    |

| Digital Inputs                    | CSB, EN, SCLK, SI, IH[1–3], IL[1–3] | -0.3 to 40                     | V    |

| Open Drain Voltage                | VMCRES, RXD, DIAG                   | -0.3 to 40                     | V    |

| Digital Output Voltage            | SO                                  | –0.3 to V <sub>VCC</sub> +0.3  | V    |

| Current Sense Input               | ISP, ISN                            | –3 to V <sub>V3RI</sub> +0.3   | V    |

| Analog Output                     | ISO, AOUT                           | -0.3 to V <sub>V3RO</sub> +0.3 | V    |

| High-side Output to GND           | GH[1–3]                             | -3 to 40                       | V    |

| Motor Phase                       | SH[1-3]                             | -3 to 40                       | V    |

| Low-side Output to GND            | GL[1-3]                             | -3 to 40                       | V    |

| Low-side Source Pin to GND        | SL[1-3]]                            | -3 to 40                       | V    |

| Voltage between HS Gate and Phase | GH[n] to SH[n] for n = {1,2,3}      | -0.3 to 20                     | V    |

| Allowable Power SQFP48K           | at 70°C                             | 2430                           | mW   |

| Thermal Resistance                | J <sub>A</sub> = Junction Ambient   | 33                             | °C/W |

| (JESD51-7)                        | J <sub>C</sub> = Junction Case      | 2                              | °C/W |

| Storage Temperature               |                                     | -55 to 150                     | °C   |

| Junction Temperature              | 1                                   | -40 to 150                     | °C   |

|                                   | (Note 1)                            | 150 to 175                     | °C   |

| ESD Human Body Model              | AEC Q100_002                        | 2                              | kV   |

| ESD Charge Device Model           | AEC Q100_011                        | 750                            | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Operation outside the Operating Junction temperature is not guaranteed. Operation above 150°C should not be considered without a written agreement from ON Semiconductor Engineering staff.

#### Table 3. ELECTRICAL CHARACTERISTICS

(Valid at a junction temperature range from  $-40^{\circ}$ C to  $150^{\circ}$ C, for supply Voltage 8.0 V  $\leq$  VS  $\leq$  25 V unless otherwise specified. Typical values at 25°C and VS = 12 V unless specified otherwise)

| Parameter                                            | Symbol  | Condition                                                                            | Min    | Тур | Max            | Unit |

|------------------------------------------------------|---------|--------------------------------------------------------------------------------------|--------|-----|----------------|------|

| SUPPLY VS RELATED INPUT                              | S       |                                                                                      |        |     |                |      |

| VS supply voltage range                              | VSLOF   | Full logic functionality                                                             | 4.5    |     | 40<br>(Note 3) | V    |

|                                                      | VSNO    | Standard FET operation mode<br>(VGVSEL = 0)                                          | 8      |     | 28<br>(Note 2) | V    |

|                                                      | VSLO    | Logic level FET operation mode<br>(VGVSEL = 1)                                       | 6      |     | 33<br>(Note 2) | V    |

| VS supply current                                    | ISTBY   | Standby mode, VS & VGIN shorted<br>VS = 6 V ~ 25 V                                   | 7      | 11  | 16             | mA   |

|                                                      | ISLEEP  | Sleep mode at 25°C, VS & VGIN shorted                                                |        | 25  | 50             | μA   |

| WAKE input voltage                                   | VTHWKL  | Low level                                                                            | 0      |     | 1.3            | V    |

|                                                      | VTHWKH  | High level                                                                           | 2.7    |     | VS             | V    |

| WAKE pulldown resistor                               | RPDWK   |                                                                                      | 50     | 100 | 200            | kΩ   |

| WAKE up time for POR                                 | TWTPOR  | WAKE pin high                                                                        |        |     | 1              | ms   |

| VCC start-up time to active state                    | TVCSU   |                                                                                      |        |     | 1.05           | ms   |

| VG start–up time to active state                     | TVGSU   |                                                                                      |        |     | 1.05           | ms   |

| OTP download time                                    | TDNLD   | After POR                                                                            |        |     | 125            | μs   |

| PWMIN switching levels                               | VTHPIL  | Low level                                                                            | 0      |     | 0.4×VS         | V    |

|                                                      | VTHPIH  | High level                                                                           | 0.6×VS |     | VS             | V    |

| PWMIN pulldown resistor                              | RPDPI   |                                                                                      | 50     | 100 | 200            | kΩ   |

| PWMIN frequency range                                | FPWMIN  |                                                                                      | 0      |     | 30             | kHz  |

| INTERNAL REGULATOR                                   | •       |                                                                                      |        |     |                |      |

| V3RO output voltage                                  | V3RO    | V3RO only connect to V3RI                                                            | 3.135  | 3.3 | 3.465          | V    |

| Max pull-up current Isource                          | IV3RO   | Source, V3RO = V3RI                                                                  |        |     | 1              | mA   |

| VCC CONSTANT VOLTAGE C                               | UTPUT   |                                                                                      |        |     |                |      |

| Output voltage 5 V                                   | VC5RO   | VCVSEL = 1, No load                                                                  | 4.9    | 5.0 | 5.1            | V    |

| Output voltage 3.3 V                                 | VC3RO   | VCVSEL = 0, No load                                                                  | 3.23   | 3.3 | 3.37           | V    |

|                                                      | VC3RL   | VS = 4.5 V, I <sub>VCC</sub> =-50 mA                                                 | 3.0    |     |                | V    |

| Voltage regulation                                   | VCCVR   |                                                                                      |        |     | 50             | mV   |

| Load regulation                                      | VCCLR   | Io = -5 mA to -50 mA                                                                 |        |     | 80             | mV   |

| Output current limit                                 | VCCILIM |                                                                                      | 50     |     | 180            | mA   |

| GATE DRIVERS                                         |         |                                                                                      |        |     |                |      |

| Low-side Rdson to SL[1-3]                            | RONLSSK | "L" level lo = 10 mA                                                                 |        | 6   | 15             | Ω    |

| Low-side Rdson to SH[1-3]                            | RONLSSC | "H" level lo = -10 mA                                                                |        | 12  | 22             | Ω    |

| High-side Rdson to SH[1-3]                           | RONHSSK | "L" level lo = 10 mA                                                                 |        | 6   | 15             | Ω    |

| High-side Rdson to BS[1-3]                           | RONHSSC | "H" level lo = -10 mA                                                                |        | 12  | 22             | Ω    |

| Propagation delay ON                                 | PDON    | 50% IHx to 20% GHx. Cload = 0 nF                                                     |        |     | 120            | ns   |

| Propagation delay OFF                                | PDOFF   | 50% IHx to 80% GHx. Cload = 0 nF                                                     |        |     | 120            | ns   |

| Propagation delay ON<br>Difference GH[1–3], GL[1–3]  | DPDON   | a.3 Phase difference of GH1,Gh2 and GH3.<br>b.3 Phase difference of GL1,GL2 and GL3. | -20    |     | 20             | ns   |

| Propagation delay OFF<br>Difference GH[1–3], GL[1–3] | DPDOFF  | a.3 Phase difference of GH1,Gh2 and GH3.<br>b.3 Phase difference of GL1,GL2 and GL3. | -20    |     | 20             | ns   |

| Output current limit                                 | IGOLIM  |                                                                                      |        | 400 |                | mA   |

| FDTI programmable dead time                          | TFDTI   | 0.2 μs step by FDTI register 4 bits (Note 4)                                         | 0.2    |     | 3.2            | μS   |

#### Table 3. ELECTRICAL CHARACTERISTICS (continued)

Pull-up resistance to VCC

RPDAL

(Valid at a junction temperature range from  $-40^{\circ}$ C to  $150^{\circ}$ C, for supply Voltage 8.0 V  $\leq$  VS  $\leq$  25 V unless otherwise specified. Typical values at 25°C and VS = 12 V unless specified otherwise)

| Parameter                                    | Symbol         | Condition                                         | Min      | Тур  | Max      | Unit  |

|----------------------------------------------|----------------|---------------------------------------------------|----------|------|----------|-------|

| BS PINS                                      |                |                                                   |          |      |          |       |

| BS internal current                          | IBSC           |                                                   |          |      | 800      | μΑ    |

| VG PIN                                       |                |                                                   |          |      |          |       |

| VG output voltage                            | VGNO           | Normal mode, VGVSEL = 0, IVG < 40 mA              | 7.0      | 11.0 | 12.0     | V     |

|                                              | VGLO           | Logic level mode, VGVSEL = 1                      | 5        | 6    | 7        |       |

|                                              | VGOL           | VS = 6 V, IVG < 30 mA                             | 5        |      |          |       |

| VG current limit                             | VGILIM         |                                                   | 40       |      | 180      | mA    |

| ANALOG OUTPUT (AOUT)                         |                |                                                   |          |      |          | -     |

| BEMF divider ratio                           | BEMFDR         |                                                   |          | 1/16 |          |       |

| BEMF divider mismatch                        | BEMFDM         |                                                   | -2       |      | 2        | %     |

| BEMF divider settling time                   | BEMFST         | for 20% to 80% step                               |          | 0.5  | 2        | μs    |

| VDH divider ratio                            | VDHDR          |                                                   |          | 1/32 |          |       |

| VDH divider settling time                    | VDHST          | for 20% to 80% step                               |          | 0.5  | 2        | μs    |

| Thermal voltage                              | VTMPH          | Tj = 155°C (Note 4)                               |          | 705  |          | mV    |

| Thermal slope                                | VTEMPSL        | (Note 4)                                          |          | +1.9 |          | mV/°C |

| AOUT full scale range                        | AOFLSCR        |                                                   |          |      | 2.1      | V     |

| AOUT output resistance                       | RONAO          | IAOUT = ±100 μA                                   |          |      | 200      | Ω     |

| AOUT output current                          | IAO            | ·                                                 | -100     |      | 100      | μA    |

| CURRENT SENSING (ISP, ISN,                   | ISO)           |                                                   |          |      |          |       |

| ISP, ISN input current                       | IISP/N         | $-0.2V \le VISP, VISN \le 2V$                     | -50      |      | 50       | μA    |

| Reference voltage ISO                        | VRCSA0         | CSOFEN = 0, GAIN = 30, ISP = ISN = 0.2 V          | 1.425    | 1.5  | 1.575    | V     |

| 0                                            | VRCSA1         | CSOFEN = 1, GAIN = 30, ISP = ISN = 0.2 V          | 0.125    | 0.2  | 0.275    | V     |

| Gain                                         | CSAG00         | CSGAIN = 00                                       | 6.53     | 7.5  | 8.63     |       |

|                                              | CSAG01         | CSGAIN = 01 (Note 4)                              |          | 15   |          |       |

|                                              | CSAG10         | CSGAIN = 10 (Note 4)                              |          | 22.5 |          |       |

|                                              | CSAG11         | CSGAIN = 11                                       | 26       | 30   | 34.3     |       |

| Common mode range                            | CSACMR         |                                                   | -0.2     | 1    | 2        | V     |

| ISN, ISP differential voltage                | DVCSAIN        |                                                   | -200     |      | 200      | mV    |

| ISO full scale range                         | CSAFLSCR       |                                                   | 0.1      |      | 2.9      | V     |

| Amplifier settling time (20% –<br>80% FSR)   | CSAOST         | Gain = 7.5, 0.25 V < V <sub>ISO</sub> < 3 V       |          |      | 5400     | ns    |

| ISO output resistance                        | RCSAO          | I <sub>ISO</sub> = ±100 μA                        |          |      | 200      | Ω     |

| ISO output current                           | ICSAO          |                                                   | -100     |      | 100      | μΑ    |

| Overcurrent voltage level VISP-              | VTHCSA00       | OCDL = 00                                         | 180      | 200  | 220      | mV    |

| V <sub>ISN</sub>                             | VTHCSA01       | OCDL = 01                                         | 130      | 150  | 170      | mV    |

|                                              | VTHCSA1X       | OCDL = 10,11                                      | 80       | 100  | 120      | mV    |

| OCMASK programmable<br>Overcurrent Mask time | TOCMASK        | 0.2 μs step by OCMASK register 4 bits<br>(Note 4) | 0.2      |      | 3.2      | μs    |

| ACTIVE HIGH DIGITAL INPUT                    | S (EN, SCLK,   | SI, IH[1–3])                                      |          |      |          |       |

| High-level input voltage                     | VTAHH          |                                                   | 0.8×V3RO |      |          | V     |

| Low-level input voltage                      | VTAHL          |                                                   |          |      | 0.2×V3RO | V     |

| Pull-down resistance                         | RPDAH          |                                                   | 50       | 100  | 200      | kΩ    |

| ACTIVE LOW DIGITAL INPUTS                    | 6 (CSB, IL[1-: | 3])                                               |          |      |          |       |

| High-level input voltage                     | VTALH          |                                                   | 0.8×V3RO |      |          | V     |

| Low-level input voltage                      | VTALL          |                                                   |          |      | 0.2×V3RO | V     |

|                                              |                |                                                   |          | 20   | 60       |       |

15

30

60

kΩ

#### Table 3. ELECTRICAL CHARACTERISTICS (continued)

(Valid at a junction temperature range from  $-40^{\circ}$ C to  $150^{\circ}$ C, for supply Voltage 8.0 V  $\leq$  VS  $\leq$  25 V unless otherwise specified. Typical values at  $25^{\circ}$ C and VS = 12 V unless specified otherwise)

| Parameter                                 | Symbol       | Condition                                                                  | Min                   | Тур  | Max   | Unit |

|-------------------------------------------|--------------|----------------------------------------------------------------------------|-----------------------|------|-------|------|

| DIGITAL OUTPUTS (SO)                      |              |                                                                            |                       |      |       |      |

| Output voltage                            | VSOH         | lo = -1 mA                                                                 | V <sub>VCC</sub> -0.2 |      |       | V    |

|                                           | VSOL         | lo = 1 mA                                                                  |                       |      | 0.2   | V    |

| OPEN DRAIN OUTPUTS (VMC                   | RES, DIAG, F | RXD)                                                                       |                       |      |       |      |

| Output voltage                            | VODL         | lo = 1 mA                                                                  |                       |      | 0.2   | V    |

| Pin leakage current                       | ILKOD        | Vo = 5.5 V                                                                 |                       |      | 10    | μΑ   |

| WARNING AND PROTECTION                    |              |                                                                            |                       |      |       |      |

| Thermal warning                           | TWT0         | THTSEL = 0                                                                 | 125                   |      |       | °C   |

| (Junction temperature)                    | TWT1         | THTSEL = 1                                                                 | 150                   |      |       | °C   |

|                                           | HYSTW        | Hysteresis                                                                 |                       | 25   |       | °C   |

| Thermal shutdown                          | TSDT0        | THTSEL = 0                                                                 | 150                   |      |       | °C   |

| (Junction temperature)                    | TSDT1        | THTSEL = 1                                                                 | 175                   |      |       | °C   |

|                                           | HYSTSD       | Hysteresis                                                                 |                       | 25   |       | °C   |

| VS voltage warning/protection             | VSOVTH       | VS high voltage detection, warning/protec-<br>tion response set by VSOVPS  | 16                    | 17   | 18    | V    |

|                                           | VSUVTH       | VS low voltage detection, warning/protec-<br>tion response set by VSUVPS   | 7                     | 7.5  | 8     | V    |

| VDH voltage warning/protection            | VDHOVTH      | VDH high voltage detection, warning/protec-<br>tion response set by VDOVPS | 25                    | 26.5 | 28    | V    |

| VG undervoltage                           | VGNUVTH      | Normal mode, VGVSEL = 0                                                    | 5                     | 6    | 7     | V    |

|                                           | VGLUVTH      | Logic level mode, VGVSEL = 1                                               | 3.5                   | 4    | 4.5   | V    |

| VCC undervoltage                          | VC3UVTH      | VCVSEL = 0                                                                 | 2.3                   |      | 2.7   | V    |

| 5                                         | VC5UVTH      | VCVSEL = 1                                                                 | 3.8                   |      | 4.2   | V    |

| V3R Power on Reset                        | VPOR         |                                                                            |                       |      | 2.7   | V    |

| FET short detection Level                 | VFSDL        | 100 mV step by FSDL register 4 bits (Note 4)                               | 100                   |      | 1600  | mV   |

| FET short Detection level                 | FSDL0000     | FSDL = 0000                                                                | 75                    | 100  | 125   | mV   |

|                                           | FSDL0010     | FSDL = 0010                                                                | 240                   | 300  | 360   | mV   |

|                                           | FSDL0100     | FSDL = 0100                                                                | 400                   | 500  | 600   | mV   |

|                                           | FSDL1000     | FSDL = 1000                                                                | 720                   | 900  | 1080  | mV   |

|                                           | FSDL1111     | FSDL = 1111                                                                | 1280                  | 1600 | 1920  | mV   |

| FET short detection masking time          | TFSDT        | 3.2 µs step by FSDT register 2 bits (Note 4)                               | 3.2                   |      | 12.8  | μS   |

| FET short detection debounce filter time, | TFSFT        | 0.8 $\mu s$ step by FSFT register 2 bits (Note 4)                          | 0.8                   |      | 3.2   | μS   |

| WATCHDOG                                  |              | •                                                                          |                       |      |       |      |

| WD first open window                      | WDFOW        | WDTWT[2:0] typical values                                                  | 3.2                   |      | 409.6 | ms   |

| WD closed window time                     | WDCW         | WDTWT[2:0] typical values                                                  | 0.8                   |      | 102.4 | ms   |

| WD open window time                       | WDOW         | WDTWT[2:0] typical values                                                  | 1.6                   |      | 204.8 | ms   |

| WD reset duration                         | WDRD         |                                                                            |                       | 400  |       | μs   |

| SPI INTERFACE                             |              |                                                                            | 1                     |      |       | 1.5  |

#### SPI INTERFACE

| SPI clock frequency | FSPI |  | 4.5 | MHz |

|---------------------|------|--|-----|-----|

| BS internal current | IBSC |  | 800 | μΑ  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

VDH overvoltage warning will be issued for elevated VS supply voltage levels. See the specification of the VDH overvoltage warning threshold voltage VDHOVTH.

3. Valid for limited time duration of 400 ms (Load dump)

4. Not tested in production. Guaranteed by design and verified during qualification.

#### DETAILED FUNCTIONAL DESCRIPTION

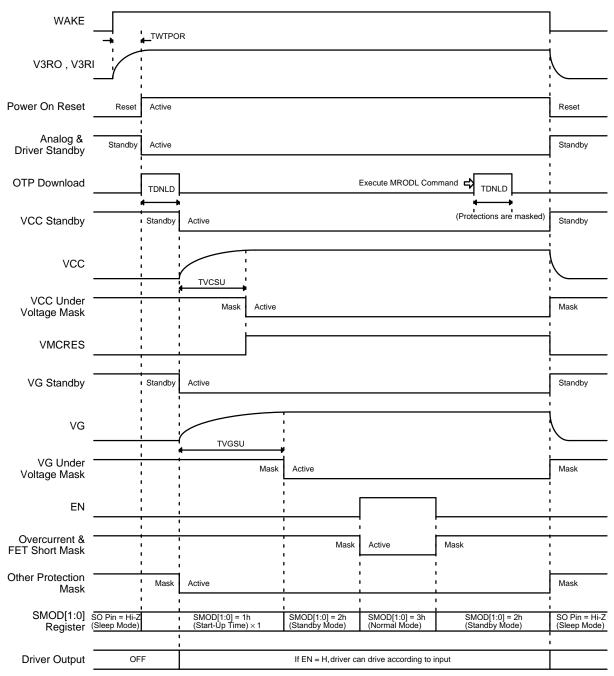

#### Chip Activation, System States and Shutdown (EN, WAKE)

Once the supply voltage VS rises above VSLOF(Min.), the LV8968BB enters Sleep mode. In Sleep mode system states are controlled with pin WAKE.

| Mode    | WAKE | EN | V3RO    | Logic  | VCC     | VG      | SPI     | Drivers |

|---------|------|----|---------|--------|---------|---------|---------|---------|

| Sleep   | L    | NA | Disable | Reset  | Disable | Disable | Disable | High–Z  |

| Standby | Н    | L  | Enable  | Active | Enable  | Enable  | Enable  | Low     |

| Normal  | NA   | Н  | Enable  | Active | Enable  | Enable  | Enable  | Active  |

#### Table 4. OPERATION MODES

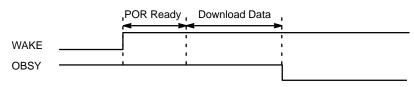

A high level on WAKE pin activates the IC from sleep mode and enables the internal linear regulator at V3RO. Once the voltage on V3RO as sensed on V3RI has passed the power on reset (POR) threshold the system oscillator starts, and releases the internal digital reset. OTP register contents are loaded into the system registers defining the power on state of the LV8968BB and the VCC regulator voltage.

VCC is powering up next, holding the CPU reset line VMCRES low until VCC passes its undervoltage level. During the entire wake–up sequence, DIAG is masked for VG undervoltage. After wake–up is complete, the IC enters Standby mode and DIAG is activated to display internal errors. During Standby mode full SPI access is possible. Note that if the CPU watchdog was enabled via OTP, a VMCRES low will be asserted after the watchdog first open window (WDFOW) unless the watchdog is being triggered properly. See section "Watchdog".

A high on EN takes the LV8968BB from Standby to Normal mode. Normal mode allows motor control and the IC accepts control inputs via the motor control pins IH[1–3], IL[1–3]. A low on EN disables the motor stage regardless of the PWM input and returns the part back to Standby mode.

The IC is shut down by taking WAKE pin low if EN is low. If EN is high, a low on WAKE will be ignored until the microcontroller pulls EN low.

NOTE: Even if EN = H, driver status is not changed to normal mode.

#### Figure 5. Powerup and Shutdown Timing

#### **Operating Voltage Range**

Normal operation with full functionality is guaranteed from 8 V to 25 V. The device will operate from 4.5 V to 40 V with limited performance:

### Shutdown: VS < VSLOF<sub>(min)</sub>

The IC will be off. Gate drivers are Hi–Z.

#### *Undervoltage: VSLOF*<sub>(min)</sub> < *VS* < *VSUVTH*

VS undervoltage warning/protection will be active according to VSUVPS. VG undervoltage warning may be asserted. If VCC is programmed to provide 3.3 V to the microcontroller, it will be supplied even if  $VS < VSLO_{(min)}$ . If motor operation is required during Undervoltage, see section below "Motor Operation during Undervoltage".

#### *Normal VS Drive Mode: VSUVTH < VS < VSOVTH* Normal operation.

*VS High Voltage Operation: VSOVTH < VS < VDHOVTH* Normal operation: VS high voltage warning/protection might be active according to VSOVPS.

#### VDH High Voltage Operation:

$VDHOVTH < VS < VSLOF_{(max)}$

VDH high voltage warning/protection might be active according to VDOVPS. The driver stage can be programmed to let the motor freewheel to protect the bootstrap circuitry at BS[1-3] from overstress. This works if the motor is not operating in field weakening.

In case of active braking, or field weakening operation, the microcontroller will have to react to a VDH overvoltage warning by either disabling the driver stage or activating all low-side FETs to brake the motor. The maximum allowed VS level for motor operation depends on the driver FET type: VSNO(Max.) or VSLO(Max.). For additional protection add zener diodes to the bootstrap pins.

#### Motor Operation during Undervoltage

An undervoltage charge pump is not included into the LV8968BB to save cost. If undervoltage operation of the motor is desired either an external charge pump must be inserted between VS and VGIN, or it is possible to use the device in logic level mode by setting MRCONF0[1]. In the latter case logic level FETs must be used for the inverter stage.

#### **System Power Supplies**

Three power supplies are integrated into the LV8968BB, all are supplied by VS:

- An internal 3.3 V regulator which provides power to the digital and interface section

- A linear regulator to provide 5 V or 3.3 V for external loads such as a microcontroller

• The VG regulator for the gate voltages of the inverter stage

#### Internal Regulator (V3RO, V3RI)

The internal regulator provides 3.3 V at V3RO and takes its feedback from V3RI. V3RO and V3RI need to be connected externally and decoupled with capacitor to GND for stability.

#### LDO 3.3 / 5 V (VCC)

VCC becomes active during Start–Up, where after Standby mode is entered. The VCC voltage can be configured via registers to provide 5 V or 3.3 V. VMCRES low is asserted if the output voltage drops below the threshold levels. VCC may power external loads and must be decoupled to GND with an external capacitor. The voltage level is programmed in register VCVSEL with OTP backup.

#### Gate Voltage Regulator (VGIN,VG)

The gate voltage regulator is supplied by VGIN and regulates to either VGNO or VGLO at VG. The voltage level is programmed in register VGVSEL with OTP backup.

VG provides the drive voltage for the low-side drivers GL[1-3] directly and for the high-side drivers BS[1-3] through the bootstrap circuitry. The output is current limited to 40 mA(min). The output at VG should be decoupled with a capacitor  $C_{VG}$  to GND which should be at least 20 times the maximum gate charge of the power FETs.

#### **Motor Control Inputs**

Once the LV8968BB is in standby mode with the supplies running, a microcontroller can facilitate motor control via the inputs EN, IL[1-3], IH[1-3]. All are VS compatible.

#### PWM Interface (PWMIN, RXD)

The PWM interface translates a VS level signal with a threshold of 40% and 60% VS to a digital signal appearing at RXD. This RXD signal can be used for input PWM signal translation to the microcontroller.

Case of abnormal state such as PWMIN pin is Open or Short, RXD signal shows Low DC voltage level.

Additionally, PWMIN a supply level compatible level shifter can bring a high voltage control such as a PWM signal or a crash indicator to microcontroller supply level.

#### Drive Enable (EN)

Taking EN high enables the output drivers GH[1-3] and GL[1-3] for control by the microcontroller, taking EN low disables them by switching all of them to the sources of the corresponding external FETs. In addition, a high on EN will override a low on WAKE allowing the microcontroller to keep the motor running even after the WAKE line has gone low.

#### Motor Control (IL[1-3] IH[1-3])

The individual motor phases are controlled by inputs IL[1–3] and IH[1–3]. IH[1–3] are active high, while IL[1–3] are active low allowing for parallel control with only three PWM outputs using internal dead time. To control the driver stage with GH [1–3] and GL[1–3] EN has to be "high". The LV8968BB will insert an adjustable dead time during output transitions to prevent short circuiting the FETs. Two drive modes exist:

#### Table 5. DRIVE 6 MODE

#### Drive 6 Mode

In drive 6 mode, each input independently controls its corresponding output requiring 6 independent PWM channels in the microcontroller. A "high" on IH1 will result in a "high" on GH1. A "high" on IL1 will result in a "low" on GL1, and so forth. Trying to force a short by driving IH1 high and IL1 low will be ignored by the logic of the LV8968BB.

| In      | put     | Output  |         |  |

|---------|---------|---------|---------|--|

| IH[1–3] | IL[1–3] | GH[1–3] | GL[1–3] |  |

| L       | L       | L       | н       |  |

| L       | Н       | L       | L       |  |

| Н       | L       | L       | L       |  |

| Н       | Н       | Н       | L       |  |

Drive 3 Mode

This mode is suitable for small microcontrollers which do not have 6 dedicated PWM control lines. IL[1-3] serve as enable signals for the phase drivers GH[1-3] and GL[1-3]

while IH[1-3] serve as their PWM inputs. Connect the microcontroller's PWM line to IH[1-3] and the phase select lines to the individual IL inputs 1-3 respectively.

#### Table 6. DRIVE 3 MODE

| h       | nput           | Output |         |  |

|---------|----------------|--------|---------|--|

| IH[1–3] | H[1–3] IL[1–3] |        | GL[1–3] |  |

| L       | L              | L      | L       |  |

| L       | Н              | L      | Н       |  |

| Н       | L              | L      | L       |  |

| Н       | Н              | Н      | L       |  |

#### Gate Drive

The gate drive circuit of the LV8968BB includes 3 half-bridge drivers which control six external N-Channel FETs. The high-side gate drivers GH[1-3] switch their gate connection either to corresponding BS[1-3] pin or the respective phase connection SH[1-3]. The low-side gate drivers GL[1-3] are switched from VG to the corresponding source connection SL[1-3]. Both high- and low-side switches are hard switching, but saturate around IGOLIM for pullup/down currents. Slope control has to be implemented with gate resistors.

#### "Through Current Prevention Function"

Current shoot through protection of the bridge drivers is implemented by ignoring inputs at IH[n] and IL[n] that would result in turning on of both high–and low–side FET at the same time. In addition a dead time counter is implemented that begins counting after one driver has been turned off, and blocks the turning–on of the complementary driver for a programmable time t<sub>FDTI</sub>.

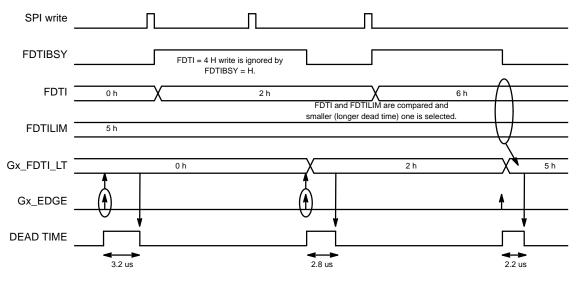

#### Dead Time Counter

The dead time counter uses a fixed minimum dead time which can be programmed into 4bit parameter FDTILIM. The dead time is never allowed to fall below that value.

A dynamic dead time register FDTI allows dead time variation during motor operation. This register is uploaded at the beginning of every dead time measurement. Flag FDTIBSY is high when a dead time value has been written to register FDTI but was not uploaded to the counter, yet. Two consecutive writes to FDTI before a counter upload are flagged as an SPI error by setting bit SACF in the SPI status register GSDAT.

Figure 6. Dead Time Programming

#### Short Protection

To protect against FET shorts the drain–source voltage of the active external power FETs is monitored. The drain source voltage of the high–side FETs is monitored between VDH and the corresponding source SH[1–3]. While the low–side FETs are monitored between SH[1–3] and SL[1–3]. After activation of the FET the short detection is masked for time t<sub>FSFT</sub> to allow for signal settling. If after the masking time t<sub>FSFT</sub> the FET voltage exceeding V<sub>FSDL</sub> continues for t<sub>FSDT</sub>, a FET short error is flagged. For details see "System Errors and Warnings" on page 18.

Four bits register FSDL selects the FET short protection shutoff voltage VFSDL. The masking time TFSDT is set with bits FSDT[1:0] and a debounce filter time TFSFT is set with bits FSFT[1:0]. Both parameters residing in register MRCONF6. These registers are dynamic and FSDL can be changed during motor operation, though FSFT and FSDT can be changed when EN = L.

#### Current Sensing and Overcurrent Shutoff

Single shunt current sensing can be implemented with the integrated high speed sense amplifier. It amplifies the voltage across ISP – ISN with a programmable gain defined by register CSGAIN. Access to this register is dynamic, allowing gain adjustment during motor operation. The offset

is determined by CSOFEN relative to an internal reference which can be either 200 mV(typ) for unidirectional current sensing, or 1.5 V(typ) for sensing current in both directions. The output of the current sense amplifier appears on the ISO pin.

#### **Overcurrent Shutoff**

A parallel path implements fast overcurrent shutoff of the driver stage. Overcurrent shutoff is triggered if the voltage across ISP – ISN exceeds a programmable level as defined by register OCDL. In overcurrent shutoff all gate drivers go to Hi–Z, turning the power FETs high impedance and letting the motor freewheel – this reaction is maskable. For more information on masking and recovery see section "System Errors and Warnings" on page 18.

To suppress switching transients, an overcurrent masking time can be programmed into register OCMASK.

#### Temperature Sensing

The LV8968BB monitors internal junction temperature  $T_j$ . The voltage representing this temperature  $(V_{PTAT})$  can be sampled at AOUT as described below. Thermal warnings and errors are issued if  $T_J$  exceeds the levels defined by THTSEL:

| THTSEL | Thermal Warning | Thermal Shutoff |

|--------|-----------------|-----------------|

| 0      | 125°C           | 150°C           |

| 1      | 150°C           | 175°C           |

If thermal error shutoff is activated, VG and VCC turn off, and the driver stage goes high impedance. As a result VMCRES goes low and SPI communication is disabled as well. The exact failure modes and masks are described in section "System Errors and Warnings".

#### **BEMF** and other Measurements

The LV8968BB includes a multiplexer for measuring the phase voltages, the motor voltage and the IC temperature. Depending on the state of AOUTSEL the following voltages appear on AOUT:

| MRAOSEL[2:0] | Pin | Formula                                                       | Comment                       |

|--------------|-----|---------------------------------------------------------------|-------------------------------|

| 0            | VDH | $V_{VDH} = 32 V_{AOUT}$                                       | Motor Supply Voltage          |

| 1            | SH1 | V <sub>SH1</sub> = 16 V <sub>AOUT</sub>                       | Phase Voltage 1               |

| 2            | SH2 | V <sub>SH2</sub> = 16 V <sub>AOUT</sub>                       | Phase Voltage 2               |

| 3            | SH3 | V <sub>SH2</sub> = 16 V <sub>AOUT</sub>                       | Phase Voltage 3               |

| 4, 5         | -   | $T_{J}(^{\circ}C) = 0.53 \text{ x V}_{AOUT}(\text{mV}) - 216$ | Internal junction temperature |

| 6, 7         | -   | High Impendance                                               |                               |

#### Table 8. AOUT SELECTION

#### Watchdog

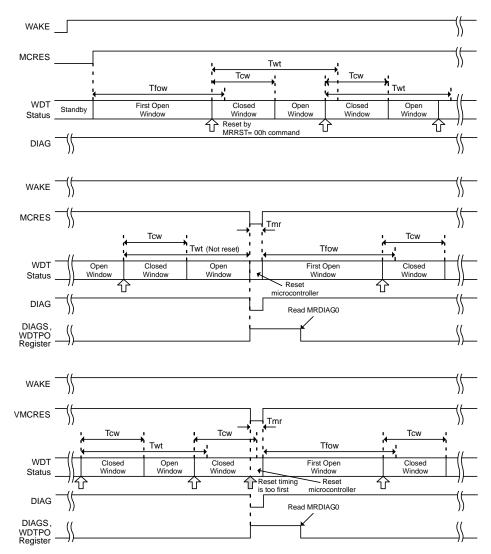

The LV8968BB includes a window watchdog to monitor the microcontroller. The size of the watchdog window is defined by register WDTWT. For detailed timing information see Figure 7: Window Watchdog Timing. A write access to register MRRST during open window time resets the watchdog timer and it starts counting again. The watchdog will issue an error whenever MRRST is written to during closed window time or the watchdog time expires. Watchdog error effects can be customized. For detailed error behavior a masking see section "System Errors and Warnings".

After a watchdog induced microcontroller reset, the error register contents of registers MRDIAG[0] remain conserved until an SPI read access. This helps the microcontroller identify the fault condition.

Figure 7. Window Watchdog Timing

| Symbol           | Characteristic                 | Min   | Тур          | Max   | Unit |

|------------------|--------------------------------|-------|--------------|-------|------|

| T <sub>FOW</sub> | WDT first open window time     |       |              |       |      |

|                  | WDTWT[2:0] = 0h                | 390.0 | 409.6        | 431.2 | ms   |

|                  | WDTWT[2:0] = 1h                | 195.0 | 204.8        | 215.6 |      |

|                  | : (1/2 step)                   | :     | : (1/2 step) | :     |      |

|                  | WDTWT[2:0] = 7h                | 3.0   | 3.2          | 3.4   |      |

| T <sub>CW</sub>  | WDT closed window time         |       |              |       |      |

|                  | WDTWT[2:0] = 0h                | 97.4  | 102.4        | 107.8 | ms   |

|                  | WDTWT[2:0] = 1h                | 48.7  | 51.2         | 53.9  |      |

|                  | : (1/2 step)                   | :     | :(1/2 step)  | :     |      |

|                  | WDTWT[2:0] = 7h                | 0.7   | 0.8          | 0.9   |      |

| T <sub>WT</sub>  | WDT window time                |       |              |       |      |

|                  | WDTWT[2:0] = 0h                | 195.0 | 204.8        | 215.6 | ms   |

|                  | WDTWT[2:0] = 1h                | 97.4  | 102.4        | 107.8 |      |

|                  | : (1/2 step)                   | :     | :(1/2 step)  | :     |      |

|                  | WDTWT[2:0] = 7h                | 1.4   | 1.6          | 1.7   |      |

| T <sub>MR</sub>  | WDT microcontroller reset time | 333   | 400          | 422   | μs   |

#### System Errors and Warnings

System errors and warnings are always flagged in their corresponding register MRDIAG0 and MRDIAG1 and their presence is indicated in SPI status register GSDAT. The LV8968BB gives great flexibility in modifying the error response. Error response definition can be backed up into OTP.

All system errors and warnings can cause a transition on DIAG. The polarity of this transition is selected in bit DIAGPOL. DIAG should be connected to an interrupt input of the microcontroller. Errors that can cause serious damage such as short–circuit and overcurrent may be latched by enabling the corresponding latch bit in MRCONF7. In this case the LV8968BB will keep the output stage disabled until the latch is cleared by one of the following actions:

- Power on reset

- EN low

- SPI write of FFh to MRRST

Table 10 explains the error behaviour. "Error" names the type of error that is covered. "Reaction Settings Option" lists which options exists for this error and the corresponding register. "Reaction names what happens if the error occurs. Some reactions depend on the "Setting Options" and are described in Notes below.

|                         |                   | Reactio       | on Setting Op     | tions           |              | Reaction |          |     |           |                       |                               |

|-------------------------|-------------------|---------------|-------------------|-----------------|--------------|----------|----------|-----|-----------|-----------------------|-------------------------------|

| Error                   | Setup<br>Register | Mask<br>Error | Report on<br>DIAG | Auto<br>Recover | Latch<br>Off | VG       | DRV      | vcc | MC<br>RES | Recovery<br>Condition | Protection<br>Enabled         |

| VS<br>Under<br>Voltage  | VSUVPS<br>[1:0]   | Yes           | Yes               | Yes             | No           | ON       | (Note 5) | ON  | Н         | VS voltage recovers   | After OTP<br>download         |

| VS Over<br>Voltage      | VSOVPS<br>[1:0]   | Yes           | Yes               | Yes             | No           | ON       | (Note 5) | ON  | Н         | VS voltage recovers   | After OTP<br>download         |

| VDH<br>Over<br>Voltage  | VDOVPS<br>[1:0]   | Yes           | Yes               | Yes             | No           | ON       | (Note 5) | ON  | Н         | VDH voltage recovers  | After OTP<br>download         |

| VG<br>Under<br>Voltage  | VGUVPS<br>[1:0]   | Yes           | Yes               | Yes             | No           | ON       | (Note 5) | ON  | Н         | VG voltage recovers   | After VG<br>start–up<br>time  |

| VCC<br>Under<br>Voltage | -                 | No            | No                | Yes             | No           | ON       | OFF      | ON  | L         | VCC voltage recovers  | After VCC<br>start–up<br>time |

Table 10. SYSTEM ERROR AND WARNING RESPONSE MATRIX

|                     |                   | Reactio       | on Setting Op     | tions           |              |          | Read     | ction    |           |                                                                                                                                                                        |                            |

|---------------------|-------------------|---------------|-------------------|-----------------|--------------|----------|----------|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Error               | Setup<br>Register | Mask<br>Error | Report on<br>DIAG | Auto<br>Recover | Latch<br>Off | VG       | DRV      | vcc      | MC<br>RES | Recovery<br>Condition                                                                                                                                                  | Protection<br>Enabled      |

| Over<br>Current     | OCPS<br>[1:0]     | Yes           | Yes               | Yes             | Yes          | ON       | (Note 5) | ON       | H         | [Latch Off]<br>EN = L or<br>execute<br>MRRST = Ffh<br>command<br>[Auto Recover]<br>EN = L or after<br>ecovery time<br>[Report]<br>EN = L or motor<br>current is down   | EN = H<br>(Normal<br>mode) |

| FET<br>Short        | FSPS<br>[1:0]     | Yes           | Yes               | Yes             | Yes          | ON       | (Note 5) | ON       | Н         | [Latch Off] EN =<br>L or execute<br>MRRST = FFh<br>command<br>[Auto Recover]<br>EN = L or after<br>recovery time<br>[Report] EN = L<br>or FET short<br>current is down | EN = H<br>(Normal<br>mode) |

| Thermal<br>Warning  | THWPS             | Yes           | Yes               | No              | No           | ON       | ON       | ON       | н         | Temperature is<br>down                                                                                                                                                 | After OTP<br>download      |

| Thermal<br>Shutdown | THSPS             | Yes           | No                | Yes             | No           | (Note 6) | (Note 6) | (Note 6) | (Note 7)  | Temperature is down                                                                                                                                                    | After OTP<br>download      |

| Watchdog<br>Timer   | WDTPS             | Yes           | No                | Yes             | No           | ON       | (Note 6) | ON       | (Note 8)  | After output<br>reset pulse from<br>VMCRES pin                                                                                                                         | VMCRES<br>= H              |

#### Table 10. SYSTEM ERROR AND WARNING RESPONSE MATRIX

Report or Ignore = ON, Latch Off or Auto Recover = OFF

Ignore = ON, Auto Recover = OFF

Ignore = H, Auto Recover = L

8. Ignore = Fixed H, Auto Recover = Output L pulse

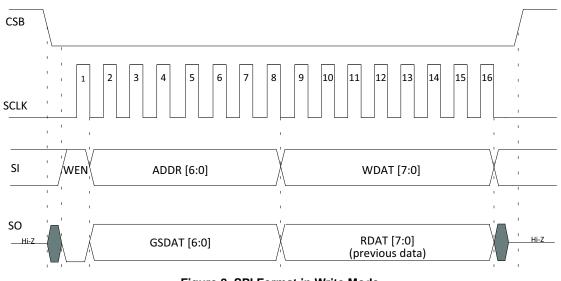

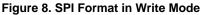

#### **SPI Interface**

In the LV8968BB the SPI Interface is used to perform general communications for status reporting, control and programming.

Figure 9. SPI Format in Read Mode

SPI communications with the LV8968BB follows established industry standard practices including the use of WEN and start and stop bits as shown above. Data is transferred MSB first and both clock and data are transferred as 'true' data with the higher level indicating a logical 1 or true state.

There are two items to be especially careful of with the general communication scheme:

- Communications must be full duplex and simultaneous. It is not allowed to send one transaction and then read data on a second transaction as the status register information will be updated on the first transaction and then be out of date for the second. Some systems break transactions into separate read and write operations which is not acceptable

- It is important the system master have the clock and data polarities and phases as shown above. Both the clock and data on some systems can be inverted for various reasons but must arrive at the LV8968BB per the above drawing. Common errors include SCLK inversion such that the leading edge arrives as a downward transition rather than a rising edge, or having the data to clock phase incorrect. Data phase must be such that the data only changes during a clock falling edge and is completely stable during a clock rising edge. This means a good margin of one half a bit time exists to eliminate transmission delay hazards.

The first byte returned on all transactions is always the status register GSDAT, and contains information such as the busy flag during programming operations

|       |       |      |       | G     | SDAT[7:0] |     |        |                                |

|-------|-------|------|-------|-------|-----------|-----|--------|--------------------------------|

| Bit 7 | 6     | 5    | 4     | 3     | 2         | 1   | Bit 0  |                                |

| 0     | ORBEN | SACF | DIAGS | LATCH | OBSY      | SMO | D[1:0] |                                |

| NA    | NA    | NA   | NA    | NA    | NA        | NA  | NA     | Sleep mode                     |

| NA    | NA    | NA   | NA    | NA    | NA        | 0   | 1      | Device start-up time           |

| NA    | NA    | NA   | NA    | NA    | NA        | 1   | 0      | Standby mode                   |

| NA    | NA    | NA   | NA    | NA    | NA        | 1   | 1      | Normal mode                    |

| NA    | 0     | 0    | 0     | 0     | 0         | NA  | NA     | Normal Operation               |

| NA    | NA    | NA   | NA    | NA    | 1         | NA  | NA     | OTP download of default values |

| NA    | NA    | NA   | NA    | 1     | NA        | NA  | NA     | Latched shutdown condition     |

| NA    | NA    | NA   | 1     | NA    | NA        | NA  | NA     | Failure Condition              |

| NA    | NA    | 1    | NA    | NA    | NA        | NA  | NA     | Last SPI access failed*        |

| NA    | 1     | NA   | NA    | NA    | NA        | NA  | NA     | OTP integrity test mode        |

Table 11.

The following SPI failures are detectable and reported collectively by a high on SACF in GSDAT[5] as general SPI failures:

- Any access to an address which is not assigned.

- The number of SCLK edges is not 16 within one word transfer

- Any access to MRCONF and ORCONF while OBSY = 1, (During write operations)

- Write access to MRODL register while OBSY = 1, (during write operations)

- Write access to any of the main registers after setting MSAENB = 1 (Implies Reg. address 04 h to 07 h are locked)

- Write access to any of the OTP registers after OSAENB = 1 (Implies Reg. address 40 h to 43 h are locked)

- Write access attempt to a read only or locked register

- SI signal changed at positive edge of SCLK (Incorrect data/sclk phase setup)

- Write access to dead time register FDTI while FDTIBSY is still high (last value has not been uploaded)

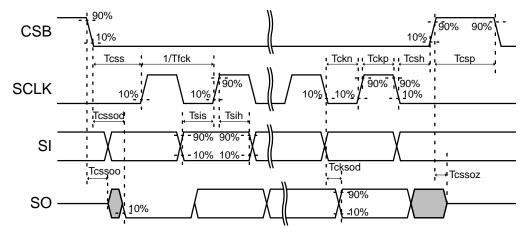

Figure 10. SPI Timing Diagram

Table 12. SPI TIMING (T<sub>J</sub> = -40 to 150°C, VS = 4.5 to 40 V, SO load = 50 pF)

| Symbol             | Comment                           | Min | Тур | Max | Unit |

|--------------------|-----------------------------------|-----|-----|-----|------|

| T <sub>FCK</sub>   | SCLK Clock Frequency              |     |     | 4.5 | MHz  |

| T <sub>CKP</sub>   | SCLK High Pulse Width             | 90  |     |     | ns   |

| T <sub>CKN</sub>   | SCLK Low Pulse Width              | 90  |     |     | ns   |

| T <sub>CSS</sub>   | CSB Setup Time                    | 90  |     |     | ns   |

| T <sub>CSH</sub>   | CSB Hold Time                     | 0   |     |     | ns   |

| T <sub>CSP</sub>   | CSB High Pulse Width              | 90  |     |     | ns   |

| T <sub>SIS</sub>   | SI Setup Time                     | 45  |     |     | ns   |

| T <sub>SIH</sub>   | SI Hold Time                      | 45  |     |     | ns   |

| T <sub>CKSOD</sub> | SCLK Fall Edge to SO Delay Time   |     |     | 75  | ns   |

| T <sub>CSSOD</sub> | CSB Fall Edge to SO Delay Time    |     |     | 75  | ns   |

| T <sub>CSSOO</sub> | CSB Fall Edge to SO Data Out Time | 0   |     |     | ns   |

| T <sub>CSSOZ</sub> | CSB Rise Edge to SO Hi–Z Out Time |     |     | 75  | ns   |

NOTE: SPI-Interface can be used after the data download of the OTP has been completed. However it can not be used during VMCRES = L.

#### **OTP** Programming

The OTP register data is typically transferred into the main registers at device start-up (From sleep to standby

transition). This operation takes up to 125  $\mu s.$  A high OBSY flag in the first returned byte during a SPI transaction indicates this.

Figure 11. OTP Data Download Timing at Start-Up

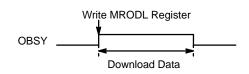

An OTP download can also actively be initiated by writing 00h to register MRODL. This command requires monitoring the OBSY flag. Don't perform specific register

access (MRCONF0 ~ 3, ORCONF0 ~ 3, MRORB, MRODL) until the OBSY flag is cleared.

Figure 12. OTP Data Download Timing after an MRODL Command

#### **OTP** Programming Overall

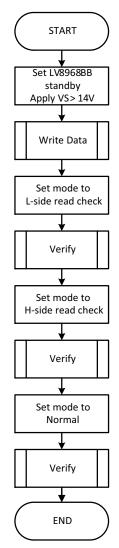

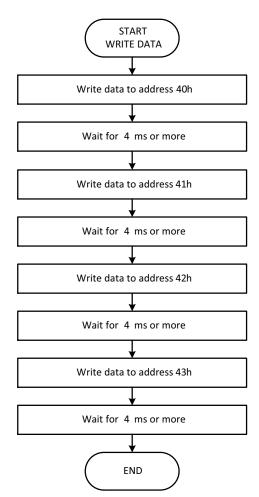

Figure 13 shows overall of the OTP memory write and verify flow. It consists of preparation, write and three times of data integrity verification.

Figure 13. OTP Memory Write and Verify Flow

#### **OTP** Programming

The OTP registers can be programmed in Standby mode only while the write lock bit OSAENB is set 0. And, the supply voltage at pin VS must be more than 14 V. The actual write operation to the OTP memory will be done, when the state change from 0 to 1 is commanded. Once the bit state is changed to 1, it cannot be change back to 0. The number of writing is limited to one per bit. The OBSY flag will be reset at the end of the write cycle. OBSY is in GSDAT register. To get GSDAT, SPI accesses to the register MRACK is recommended. MRACK doesn't interfere with the programming operation.

MRCONF0 ~ 3, ORCONF0 ~ 3, MRORB, MRODL registers cannot be accessed during an OTP write cycle.

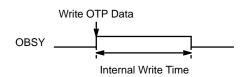

Figure 14. OTP Programming Timing

The programming takes 4 ms maximum. To simplify operation, a waiting for 4 ms plus margin can be applicable instead of a polling of the flag OBSY. (Figure 15)

#### OTP Data Integrity Verification

In order to verify that the OTP programming operation was successful. It is strongly recommended to do an OTP margin check: To do this, the OTP registers are downloaded into the main register bank with minimum and maximum readout thresholds. This OTP download is forced by writing 00h to register MRODL. The readout threshold is set in register MRORB.

- OTP Margin read check sequence after programmed:

- 1. Set OTP readout threshold "low" by setting ORBEN = 1 and ORBLV = 0 in register MRORB

- 2. Execute OTP download command by writing 00h to MRODL

- 3. Verify that the main register contents are consistent with the programmed OTP data

- 4. Set OTP readout threshold "high" by setting ORBEN = 1 and ORBLV = 1 in register MRORB

- 5. Execute OTP download command by writing 00h to MRODL

- 6. Verify that the main register contents are consistent with the programmed OTP data

- 7. Return OTP threshold to normal by setting ORBEN = 0 and ORBLV = 0

- 8. Execute OTP download command

- 9. Verify that the main register contents are consistent with the programmed OTP data

#### Locking OTP Register Contents

MSAENB bit and OSAENB bit are used in order to prevent write-access of main- and OTP registers respectively. **CAUTION:** Inadvertent writing of these bits will permanently lock the corresponding register blocks from any further write access. Should only be set at end of development cycles.

#### Table 13. REGISTER MAP

| WENB by<br>WEN (1bit) | Write Time<br>Condition | ADDR<br>[6:0] | Data<br>Name | D[7] | D[6]        | D[5]       | D[4]            | D[3]           | D[2]         | D[1]            | D[0]    |

|-----------------------|-------------------------|---------------|--------------|------|-------------|------------|-----------------|----------------|--------------|-----------------|---------|

| Don't care            | Don't care              | -             | GSDAT        | 0    | ORBEN       | SACF       | DIAGS           | LATCH          | OBSY         | SMOE            | [1:0]   |

| OSAENB<br>(Note 9)    | EN=L                    | 00h           | MRCONF0      | 0    | 0           | THTSEL     | DFCSEL          | DIAGLTO        | DIAGPOL      | VGVSEL          | VCVSEL  |

| (NOLE 9)              |                         | 01h           | MRCONF1      | 0    | 0           | 0          | WDTPS           | THSPS          | THWPS        | VGUVF           | S[1:0]  |

|                       |                         | 02h           | MRCONF2      | 0    | 0           | VDOV       | PS[1:0]         | VSOVI          | PS[1:0]      | VSUVP           | S[1:0]  |

| Read Only             | Read Only               | 03h           | MRCONF3      | 0    | 0           | 0          | 0               | 0              | 0            | 0               | OSAENB  |

| MSAENB                | EN=L                    | 04h           | MRCONF4      | 0    |             | WDTWT[2:0] |                 | 0              | CSOFEN       | AWODLEN         | D3MDEN  |

| (Note 9)              |                         | 05h           | MRCONF5      | 0    | 0 OCDL[1:0] |            |                 |                | OCMA         | SK[3:0]         |         |

|                       |                         | 06h           | MRCONF6      | 0    | 0           | 0          | 0               | FSFT           | [1:0]        | FSDT            | [1:0]   |

|                       |                         | 07h           | MRCONF7      | FSP  | S[1:0]      | OCP        | S[1:0]          | FDTILIM[3:0]   |              |                 |         |

| EN=L or H             |                         | 08h           | MRCONF8      | 0    | 0           | 0          | 0               | 0              | 0            | 0               | MSAENB  |

| EN=L or H             | EN=L or H               | 10h           | MRAOSEL      | 0    | 0           | 0          | 0               | 0              | AOUT         | SEL[2:0] (Defau | lt=7h)  |

|                       |                         | 11h           | MRCSG        | 0    | 0           | 0          | 0               | 0              | 0            | CSGAI           | N[1:0]  |

|                       |                         | 12h           | MRFSDL       | 0    | 0           | 0          | 0               |                | FSD          | L[3:0]          |         |

|                       |                         | 13h           | MRFDTI       | 0    | 0           | 0          | 0               |                | FDT          | T[3:0]          |         |

|                       |                         | 14h           | MRFDTIF      | 0    | 0           | 0          | 0               | 0              | 0            | 0               | FDTIBSY |

|                       |                         | 15h           | MRRST        |      |             | Write 00   | h: Reset WDT /  | Write FFh: Res | et latch off |                 |         |

|                       | EN=L                    | 16h           | MRORB        | 0    | 0           | 0          | 0               | 0              | 0            | ORBEN           | ORBLV   |

|                       |                         | 17h           | MRODL        |      |             | Wri        | te 00h: Execute | OTP data dow   | nload        | •               |         |

| Read Only             | Read Only               | 20h           | MRDIAG0      | 0    | 0           | 0          | WDTPO           | THSPO          | THWPO        | FSPO            | OCPO    |