#### 1. Introduction

This application note will help developers quickly implement proof-of-concept designs using the **KX134** tri-axis accelerometer. Please refer to the corresponding Technical Reference Manual document for available engines specific to your product and additional implementation guidelines. Kionix strives to ensure that our accelerometers will meet design expectations by default, but it is not possible to provide default setting to work in every environment. Depending on the intended application, it is very likely that some customization will be required to optimize performance. The information provided here will help the developer get the most out of these tri-axis accelerometers.

#### 2. Circuit Schematic

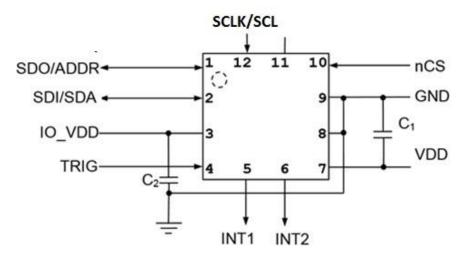

This section shows recommended wiring for this accelerometer, based on proven operation of the part. Specific applications may require modifications from these recommendations. Please refer to the corresponding Product Specifications document for all pin descriptions.

Figure 1: KX134 Application Schematic

# 3. Quick Start Implementations

Here we present several basic ways to initialize the part. These can vary based on desired operation, but generally the initial operations a developer wants to do are: 1) read back acceleration data asynchronously, 2) read back acceleration data when next data is ready via interrupt (synchronous data reading), 3) use of the sample buffer, 4) use the Wake-Up function, 5) activate the tilt position function, 6) activate the tap/double-tap function, and 7) activate the free-fall function. These cursory solutions are provided as a means for configuring the part to a known operational state. Note that these conditions just provide a starting point, and the values may vary as developers refine their application requirements.

# 3.1. Asynchronous Reading

This example configures and enables the accelerometer to start outputting sensor data that can be asynchronously read from the output registers.

Write 0x00 to Control 1 (CNTL1) to set the accelerometer in stand-by mode

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

- Write 0x06 to Output Data Control (ODCNTL) to set the Output Data Rate (ODR) of the accelerometer to 50 Hz. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| ODCNTL        | 0x21    | 0x06  |

Write 0xC0 to Control 1 (CNTL1) to set the accelerometer into operating mode (PC1=1), full power mode (RES=1), data ready disabled (DRDYE=0), range to ±8g (GSEL=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xC0  |

- Acceleration data can now be read from the XOUT\_L, XOUT\_H, YOUT\_L, YOUT\_H, ZOUT\_L, and ZOUT\_H registers in 2's complement format asynchronously. To reduce the duplicate sensor data, wait at least 1/ODR period before reading the next sample.

#### 3.2. Synchronous Reading (with hardware interrupt)

This example configures and enables the accelerometer to start outputting sensor data with a synchronous signal (DRDY) and data can read from the output registers.

Write 0x00 to Control 1 (CNTL1) to set the accelerometer in stand-by mode

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

Write 0x30 to Interrupt Control 1 (INC1) to enable physical interrupt pin INT1, set the polarity of the physical interrupt to active high and configure for latched operation (Note: if the output registers are read in a burst sequence, the latched interrupt will auto clear by default).

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x30  |

Write 0x10 to Interrupt Control 4 (INC4) to set the Data Ready interrupt to be reported on physical interrupt pin INT1.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC4          | 0x25    | 0x10  |

Write 0x06 to Output Data Control (ODCNTL) to set the Output Data Rate (ODR) of the accelerometer to 50 Hz. This step is optional as this is also a default setting.

| Register Name | Address | Value |

|---------------|---------|-------|

| ODCNTL        | 0x21    | 0x06  |

Write 0xE0 to Control 1 (CNTL1) to set the accelerometer into operating mode (PC1=1), full power mode (RES=1), data ready enabled (DRDYE=1), range to ±8g (GSEL=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xE0  |

Acceleration data can now be read from the XOUT L, XOUT H, YOUT L, YOUT H, ZOUT L, and ZOUT H registers in 2's complement format synchronously following the rising edge of INT1.

# 3.3. Synchronous Reading (<u>without</u> hardware interrupt)

This example configures and enables the accelerometer to start outputting sensor data with a synchronous signal (DRDY) and data can read from the output registers.

- Write 0x00 to Control 1 (CNTL1) to set the accelerometer in stand-by mode

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

Write 0x06 to Output Data Control (ODCNTL) to set the Output Data Rate (ODR) of the accelerometer to 50 Hz. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| ODCNTL        | 0x21    | 0x06  |

- Write 0xE0 to Control 1 (CNTL1) to set the accelerometer into operating mode (PC1=1), full power mode (RES=1), data ready enabled (DRDYE=1), range to ±8g (GSEL=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xE0  |

- Acceleration data can now be read from the XOUT\_L, XOUT\_H, YOUT\_L, YOUT\_H, ZOUT\_L, and ZOUT\_H registers in 2's complement format synchronously when the DRDY bit is set (0x10) in the Interrupt Status 2 Register (INS2).

| Register Name | Address | Value |

|---------------|---------|-------|

| INS2          | 0x17    | ins2  |

```

if (ins2 & 0x10)

{

// read output registers

}

```

# 3.4. Sample Buffer Operation

# 3.4.1. Buffer Full Interrupt (BFI)

This example configures enables the accelerometer to start outputting sensor data to the internal buffer until full. When the buffer is full, a hardware interrupt is generated and data can then be read from the buffer. The mode of operation is first in, first out (FIFO) below.

Write 0x00 to Control 1 (CNTL1) to set the accelerometer in stand-by mode

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

- Write 0x06 to Output Data Control (ODCNTL) to set the Output Data Rate (ODR) of the accelerometer to 50 Hz. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| ODCNTL        | 0x21    | 0x06  |

- Write 0x30 to Interrupt Control (INC1) to enable physical interrupt pin INT1, set the polarity of the physical interrupt to active high and configure for latched operation.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x30  |

- Write 0x40 to Interrupt Control 4 (INC4) to set the Buffer Full interrupt to be reported on physical interrupt pin INT1.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC4          | 0x25    | 0x40  |

- Write 0xE0 to Buffer Control 2 (BUF\_CNTL2) to enable the sample buffer (BUFE=1), to set the resolution of the acceleration data samples collected to 16-bit resolution (BRES=1), to enable the buffer full interrupt (BFIE=1), and set the operating mode of the sample buffer to FIFO (BM=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| BUF_CNTL2     | 0x5F    | 0xE0  |

Write 0xE0 to Control 1 (CNTL1) to set the accelerometer into operating mode (PC1=1), full power mode (RES=1), data ready enabled (DRDYE=1), range to ±8g (GSEL=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xE0  |

Once a Buffer-Full Interrupt is issued on INT1 pin, acceleration data can then be read from the Buffer Read (BUF\_READ) register at address 0x63 in 2's complement format. Since the resolution of the samples data was set to 16-bit, the data is recorded in the following order: X\_L, X\_H, Y\_L, Y\_H, Z\_L and Z\_H with the oldest data point read first as the buffer is in FIFO mode. The full buffer contains 516 bytes of data, which corresponds to 86 unique acceleration

data samples. (Note: With BRES=0 (8-bit resolution), in BUF\_CNTL2, it is possible to collect 171 samples or 513 bytes of data).

# 3.4.2. Watermark Interrupt (WMI)

This example configures enables the accelerometer to start outputting sensor data to the internal buffer until a watermark is reached. When the watermark is reached, a hardware interrupt is generated and data can then be read from the buffer. The mode of operation is first in, first out (FIFO) below.

- Write 0x00 to Control Register 1 (CNTL1) to set the accelerometer in stand-by mode

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

- Write 0x06 to Output Data Control (ODCNTL) to set the Output Data Rate (ODR) of the accelerometer to 50 Hz. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| ODCNTL        | 0x21    | 0x06  |

- Write 0x30 to Interrupt Control (INC1) to enable physical interrupt pin INT1, set the polarity of the physical interrupt to active high and configure for latched operation.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x30  |

- Write 0x20 to Interrupt Control 4 (INC4) to set the Watermark interrupt to be reported on physical interrupt pin INT1.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC4          | 0x25    | 0x20  |

Write 0x2B (43d) to set a watermark level to exactly half of the buffer.

| Register Name | Address | Value |

|---------------|---------|-------|

| BUF_CTNL1     | 0x5E    | 0x2B  |

- Write 0xE0 to Buffer Control 2 (BUF\_CNTL2) to enable the sample buffer (BUFE=1), to set the resolution of the acceleration data samples collected to 16-bit resolution (BRES=1) and set the operating mode of the sample buffer to FIFO (BM=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| BUF_CNTL2     | 0x5F    | 0xE0  |

Write 0xE0 to Control 1 (CNTL1) to set the accelerometer into operating mode (PC1=1), full power mode (RES=1), data ready enabled (DRDYE=1), range to ±8g (GSEL=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xE0  |

Once a Watermark Interrupt is issued on INT1 pin, acceleration data can then be read from the Buffer Read (BUF\_READ) register at address 0x63 in 2's complement format. The data is recorded in the following order: X\_L, X\_H, Y\_L, Y\_H, Z\_L and Z\_H (16-bit mode) with the oldest data point read first as the buffer is in FIFO mode. The full buffer contains 258 bytes of data, which corresponds to 43 unique acceleration data samples.

# 3.4.3. Trigger Mode

This example configures enables the accelerometer to start filling sensor data to the internal buffer. Prior to a trigger event, once the watermark setting is reached, old data will be discarded and new data will be added. Following a trigger event, data will continue to fill until the buffer is full. A hardware interrupt is generated when the buffer is full and data can then be read from the buffer. The mode of operation is first in, first out (FIFO). The purpose of this example is to show how data can be captured both before and after an event (external trigger, tap, wakeup, freefall).

Write 0x00 to Control 1 (CNTL1) to set the accelerometer in stand-by mode

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

- Write 0x06 to Output Data Control (ODCNTL) to set the Output Data Rate (ODR) of the accelerometer to 50 Hz. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| ODCNTL        | 0x21    | 0x06  |

- Write 0x30 to Interrupt Control 1 (INC1) to enable physical interrupt pin INT1, set the polarity of the physical interrupt to active high and configure for latched operation.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x30  |

- Write 0x40 to Interrupt Control 4 (INC4) to set the Buffer Full interrupt to be reported on physical interrupt pin INT1.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC4          | 0x25    | 0x40  |

- Write 0x2B (43d) to BUF\_CNTL1, which sets a watermark level to exactly half of the buffer.

| Register Name | Address | Value |

|---------------|---------|-------|

| BUF CNTL1     | 0x5E    | 0x2B  |

- Write 0xE2 to Buffer Control 2 (BUF\_CNTL2) to enable the sample buffer (BUFE=1), to set the resolution of the acceleration data samples collected to 16-bit resolution (BRES=1), to enable the buffer full interrupt (BFIE=1), and set the operating mode of the sample buffer to Trigger mode.

| Register Name | Address | Value |

|---------------|---------|-------|

| BUF_CNTL2     | 0x5F    | 0xE2  |

- Write 0x3F to Interrupt Control 2 (INC2) to enable all positive and negative directions that can cause a wakeup event.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC2          | 0x23    | 0x3F  |

- Write 0xAE to Control 3 (CNTL3) to set output data rate for the wakeup engine (OWUF) to 50Hz.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL3         | 0x1D    | 0xAE  |

- Write 0x60 to Control 4 (CNTL4) to set the counter mode to clear (C\_MODE=0), threshold mode to relative (TH\_MODE=1), enable the wakeup function (WUFE=1), disable the back to sleep function (BTSE=0), set pulse reject mode set to standard operation and set the output data rate for the back to sleep engine to its default of 0.781Hz.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL4         | 0x1E    | 0x60  |

- Write 0x01 to Control 5 (CNTL5) to put the sensor into sleep mode (MAN\_SLEEP=1).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL5         | 0x1F    | 0x01  |

- Write 0x05 to Wakeup Function Counter (WUFC) to set the time motion must be present for 0.1 second before a Wake-up interrupt is triggered. The following formula is used:

# WUFC (counts) = Desired Delay Time (sec) x OWUF (Hz)

$$WUFC$$

(counts) = 0.1 sec x 50 Hz = 5 counts

| Register Name | Address | Value |

|---------------|---------|-------|

| WUFC          | 0x4D    | 0x05  |

Write 0x20 to the Wakeup Function Threshold (WUFTH) and 0x00 to Back to Sleep Wakeup Function Threshold (BTSWUFTH) to set the wakeup threshold to 0.5g.

# WUFTH (counts) = Wake-Up Threshold (g) x 64 (counts/g)

WUFTH (counts) =

$$0.5g * 64 \text{ counts/}g = 32 (0x20) \text{ counts}$$

| Register Name | Address | Value |

|---------------|---------|-------|

| WUFTH         | 0x49    | 0x20  |

| BTSWUFTH      | 0x4A    | 0x00  |

- Write 0xE0 to Control 1 (CNTL1) to set the accelerometer into operating mode (PC1=1), full power mode (RES=1), data ready enabled (DRDYE=1), range to ±8g (GSEL=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xE0  |

Provide some time for the buffer to fill to the configured threshold. Assuming the default ODR was used, it should take approximately 0.86 seconds. After this time, trigger a wakeup event by shaking the unit above the configured threshold and timing settings. Next, wait for the Buffer-Full Interrupt. Once Buffer-Full Interrupt is issued on INT1 pin, acceleration data can then be read from the Buffer Read (BUF\_READ) register at address 0x63 in 2's complement format. Since the resolution of the samples data was set to 16-bit, both high and low bytes of each sample were stored in the buffer, and recorded in the following order: X\_L, X\_H, Y\_L, Y\_H, Z\_L, Z\_H with the oldest data point read first as it is a FIFO buffer. The full buffer contains 516 bytes of data, which corresponds to 86 unique acceleration data samples. The data set will include all the data prior to the trigger event, plus all the data after the event.

# 3.4.4. Buffer Reading Tips

- a) The acceleration data can be read from a buffer using multiple-byte read as shown in the Figure 2 below. The register auto-increment feature is disabled when data is read from the Buffer Read register.

- b) If data is read using single-byte read, it should be read in increments of 3 bytes in 8-bit resolution mode and 6 bytes in 16-bit resolution mode.

- c) It is very important to follow proper I2C Write-Read sequence as specified in the product specifications. More specifically, the Master should avoid sending the Stop (P) bit at the end of the I2C Write command, and should issue a Repeat Start bit (Sr) at the start of the I2C Read command as show in the Figure 2. Failure of following this sequence may result in reading the same value from the Read Buffer.

| Master | S | SAD + W |     | RA |     | Sr | SAD + R |     |      | ACK |      | NACK | Р |

|--------|---|---------|-----|----|-----|----|---------|-----|------|-----|------|------|---|

| Slave  |   |         | ACK |    | ACK |    |         | ACK | DATA |     | DATA |      |   |

| Term | Definition                |  |  |

|------|---------------------------|--|--|

| S    | Start Condition           |  |  |

| Sr   | Repeated Start Condition  |  |  |

| SAD  | Slave Address             |  |  |

| W    | Write Bit                 |  |  |

| R    | Read Bit                  |  |  |

| ACK  | Acknowledge               |  |  |

| NACK | Not Acknowledge           |  |  |

| RA   | Register Address          |  |  |

| Data | Transmitted/Received Data |  |  |

| Р    | Stop Condition            |  |  |

Figure 2: Proper I2C Sequence to Receive Data from the Slave

# 3.5. Wake-up / Back-to-Sleep Engine

# 3.5.1. Wake-up

This example configures and enables the accelerometer to detect wake-up events using an external interrupt pin with Back-to-Sleep function disabled.

Write 0x00 to Control 1 (CNTL1) to set the accelerometer in stand-by mode

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

- Write 0x06 to Output Data Control (ODCNTL) to set the Output Data Rate (ODR) of the accelerometer to 50 Hz. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| ODCNTL        | 0x21    | 0x06  |

- Write 0x30 to Interrupt Control 1 (INC1) to enable physical interrupt pin INT1, set the polarity of the physical interrupt to active high and configure for latched operation.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x30  |

- Write 0x02 to Interrupt Control 4 (INC4) to set the Wakeup Function Interrupt (WUFI1=1) to be reported on physical interrupt pin INT1.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC4          | 0x25    | 0x02  |

- Write 0x3F to Interrupt Control 2 (INC2) to enable all positive and negative directions that can cause a wakeup event.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x3F  |

- Write 0xAE to Control 3 (CNTL3) to set output data rate for the wakeup engine (OWUF) to 50Hz.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL3         | 0x1D    | 0xAE  |

Write 0x60 to Control 4 (CNTL4) to set the counter mode to clear (C\_MODE=0), threshold mode to relative (TH\_MODE=1), enable the wakeup function (WUFE=1), disable the back to sleep function (BTSE=0), set pulse reject mode to standard operation and set the output data rate for the back to sleep engine to its default of 0.781Hz.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL4         | 0x1E    | 0x60  |

Write 0x01 to Control 5 (CNTL5) to for the sensor into sleep mode (MAN\_SLEEP=1).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL5         | 0x1F    | 0x01  |

Write 0x05 to Wakeup Function Counter (WUFC) to set the time motion must be present for

0.1 second before a Wake-up interrupt is triggered. The following formula is used:

# WUFC (counts) = Desired Delay Time (sec) x OWUF (Hz)

# WUFC (counts) = 0.1 sec x 50 Hz = 5 counts

| Register Name | Address | Value |

|---------------|---------|-------|

| WUFC          | 0x4D    | 0x05  |

- Write 0x20 to the Wakeup Function Threshold (WUFTH) and 0x00 to Back to Sleep Wakeup Function Threshold (BTSWUFTH) to set the wakeup threshold to 0.5g.

# WUFTH (counts) = Wake-Up Threshold (g) x 64 (counts/g)

$$WUFTH$$

(counts) = 0.5g \* 64 counts/g = 32 (0x20) counts

| Register Name | Address | Value |

|---------------|---------|-------|

| WUFTH         | 0x49    | 0x20  |

| BTSWUFTH      | 0x4A    | 0x00  |

- Write 0xE0 to Control 1 (CNTL1) to set the accelerometer into operating mode (PC1=1), full power mode (RES=1), data ready enabled (DRDYE=1), range to ±8g (GSEL=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xE0  |

- Monitor the physical interrupt INT1 of the accelerometer, if the acceleration input profile satisfies the criteria previously established for the 0.5g motion detect threshold level in both positive and negative directions of the X, Y, Z axis for more than 0.1 second, then there should be positive latched interrupt present. Also, the WUFS bit in Interrupt Status 3 (INS3) will be set to indicate the wake-up interrupt has fired. INS3 also provides information regarding which axis/axes caused the wakeup interrupt. Finally, WAKE bit in Status (STAT) will also be set to indicate the sensor is in WAKE mode.

| Register Name | Address | Value |

|---------------|---------|-------|

| INS3          | 0x18    | ins3  |

```

if (ins3 & 0x80)

{

// handle wakeup event

}

```

- Read Interrupt Latch Release (INL\_REL) to unlatch (clear) the output interrupt created by the motion detection function and to clear the WUFS bit in the Interrupt Status 3 (INS3).

| Register Name | Address | Value |

|---------------|---------|-------|

| INT_REL       | 0x1A    | N/A   |

- Write 0x01 to Control 5 (CNTL5) to force sleep state (MAN\_SLEEP=1). With Back-to-Sleep engine disabled, this step is required in order to be able to detect additional wake-up interrupt. Note, this also clears the WAKE bit in STATUS\_REG register to indicate Back-to-Sleep state.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL5         | 0x1F    | 0x01  |

# 3.5.2. Wake-up and Back-to-Sleep

This example configures and enables the accelerometer to detect both wake-up and back-tosleep events using an external interrupt pin.

- Write 0x00 to Control 1 (CNTL1) to set the accelerometer in stand-by mode

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

- Write 0x06 to Output Data Control (ODCNTL) to set the Output Data Rate (ODR) of the accelerometer to 50 Hz. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| ODCNTL        | 0x21    | 0x06  |

- Write 0x30 to Interrupt Control 1 (INC1) to enable physical interrupt pin INT1, set the polarity of the physical interrupt to active high and configure for latched operation.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x30  |

- Write 0x0A to Interrupt Control 4 (INC4) to set the Back to Sleep Interrupt (BTSI=1) and Wakeup Interrupt (WUFI1) to be reported on physical interrupt pin INT1.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC4          | 0x25    | 0x0A  |

- Write 0x3F to Interrupt Control 2 (INC2) to enable all positive and negative directions that can cause a wakeup event.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC2          | 0x23    | 0x3F  |

- Write 0xAE to Control 3 (CNTL3) to set output data rate for the wakeup engine (OWUF) to 50Hz.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL3         | 0x1D    | 0xAE  |

- Write 0x76 to Control 4 (CNTL4) to set the counter mode to clear (C\_MODE=0), threshold mode to relative (TH\_MODE=1), enable the wakeup function (WUFE=1), enable the back to sleep function (BTSE=1), set pulse reject mode to standard operation and set the output data rate for the back to sleep engine to 50Hz.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL4         | 0x1E    | 0x76  |

- Write 0x01 to Control 5 (CNTL5) to force sleep state (MAN\_SLEEP=1). Note, this also clears the WAKE bit in STAT register to indicate Back-to-Sleep state.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL5         | 0x1F    | 0x01  |

- Write 0x05 to Back-to-Sleep Counter (BTSC) to set the time motion must be absent for 0.1 second before a Back-to-Sleep interrupt is triggered. The following formula is used:

BTSC (counts) = Desired Delay Time (sec) x OBTS (Hz) BTSC (counts) = 0.1 sec x 50 Hz = 5 counts

| Register Name | Address | Value |

|---------------|---------|-------|

| BTSC          | 0x4C    | 0x05  |

- Write 0x05 to Wakeup Function Counter (WUFC) to set the time motion must be present for 0.1 second before a Wake-up interrupt is triggered. The following formula is used:

WUFC (counts) = Desired Delay Time (sec) x OWUF (Hz) WUFC (counts) = 0.1 sec x 50 Hz = 5 counts

| Register Name | Address | Value |

|---------------|---------|-------|

| WUFC          | 0x4D    | 0x05  |

- Write 0x20 to Wakeup Function Threshold (WUFTH) and 0x00 to Back to Sleep Wakeup Function Threshold (BTSWUFTH) and 0x80 to Back to Sleep Threshold (BTSTH) to set the wakeup and back to sleep thresholds to 0.5g.

WUFTH (counts) = Wake-Up Threshold (g) x 64 (counts/g) WUFTH (counts) = 0.5g \* 64 counts/g = 32 (0x20) counts

BTSTH (counts) = Back To Sleep Threshold (g) x 64 (counts/g) BTSTH (counts) = 0.5g \* 64 counts/g = 32 (0x20) counts

| Register Name | Address | Value |  |

|---------------|---------|-------|--|

| WUFTH         | 0x49    | 0x20  |  |

| BTSWUFTH      | 0x4A    | 0x00  |  |

| BTSTH         | 0x4B    | 0x20  |  |

- Write 0xE0 to Control 1 (CNTL1) to set the accelerometer into operating mode (PC1=1), full power mode (RES=1), data ready enabled (DRDYE=1), range to ±8g (GSEL=0).

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xE0  |

Monitor the physical interrupt INT1 of the accelerometer, if the acceleration input profile satisfies the criteria previously established for the 0.5g motion detect threshold level in both positive and negative directions of the X, Y, Z axis for more than 0.1 second, then there should be positive latched interrupt present. Also, the WUFS bit in Interrupt Status 3 (INS3) will be set to indicate the wake-up interrupt has fired. INS3 also provides information regarding which axis/axes caused the wakeup interrupt. Finally, WAKE bit in Status (STAT) will also be set to indicate the sensor is in WAKE mode.

| Register Name | Address | Value |

|---------------|---------|-------|

| INS3          | 0x18    | ins3  |

```

if (ins3 & 0x80)

{

// handle wakeup event

}

```

- Read Interrupt Latch Release (INT\_REL) to unlatch (clear) the output interrupt created by the motion detection function and to clear the WUFS bit in the Interrupt Status 3 (INS3).

| Register Name | Address | Value |

|---------------|---------|-------|

| INT_REL       | 0x1A    | N/A   |

Continue to monitor the physical interrupt INT1 of the accelerometer, if the lack of acceleration input profile satisfies the criteria previously established for the 0.5g of no motion detect threshold level in both positive and negative directions of the X, Y, Z axis for more than 0.1 second, then there should be positive latched interrupt present. Also, the BTS bit in Interrupt Status 3 (INS3) will be set to indicate the back-to-sleep interrupt has fired. INS3 also provides information regarding which axis/axes caused the wakeup interrupt. Finally, WAKE bit in STATUS\_REG will also be 0 to indicate the sensor is in BACK TO SLEEP mode.

| Register Name | Address | Value |

|---------------|---------|-------|

| INS3          | 0x18    | ins3  |

```

if (ins2 & 0x40)

{

// handle back to sleep event

}

```

- Read Interrupt Latch Release (INT\_REL) to unlatch (clear) the output interrupt created by the motion detection function and to clear the WUFS bit in the Interrupt Status 3 (INS3).

| Register Name | Address | Value |

|---------------|---------|-------|

| INT_REL       | 0x1A    | N/A   |

\*Note: The sensor itself is enabled and in run mode. Back-To-Sleep state refers to lack of motion detected by the sensor that can be contributed to the object's motion is below the threshold (e.g. object is at rest).

# 3.6. Tilt Engine

#### 3.6.1. Activate Tilt Position Function with Face Detect

- Write 0x00 to Control Register 1 (CNTL1) to set the accelerometer in stand-by mode.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

- Write 0x3F to Control 2 register (CNTL2) to enable Tilt detection from positive and negative directions of all three axes (+x, -x, +y, -y, +z, -z). This step is optional as this is also a default setting.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL2         | 0x1C    | 0x3F  |

- Write 0xA8 to Control 3 register (CNTL3) to set the output data rate for the Tilt Position function to 12.5Hz. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL3         | 0x1D    | 0xA8  |

Write 0x01 to TILT\_TIMER register. Here we assume an 80 msec timer will be sufficient. Note that each count value written to this register is calculated as 1/(Tilt Position ODR) = 1/12.5Hz = 80 msec.

| Register Name | Address | Value |

|---------------|---------|-------|

| TILT_TIMER    | 0x29    | 0x01  |

- Write 0x0C to Tilt Angle Low Limit (TILT\_ANGLE\_LL) register to set the low threshold to  $22^{\circ}$  from Horizontal. The value is calculated using the following equations: TILT\_ANGLE\_LL (counts) =  $\sin \theta$  \* (32 (counts/g)). This step is optional as this is also a default setting.

| Register Name | Address | Value |

|---------------|---------|-------|

| TILT_ANGLE_LL | 0x37    | 0x0C  |

- Write 0x2A to Tilt Angle High Limit (TILT\_ANGLE\_HL) register to set the High threshold. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| TILT_ANGLE_HL | 0x38    | 0x2A  |

- Write 0x14 to HYST\_SET register to set the hysteresis that is placed between the screen rotation states to ±15°. This step is optional as this is also a default setting.

| Register Name | Address | Value |

|---------------|---------|-------|

| HYST_SET      | 0x39    | 0x14  |

- Write 0x30 to Interrupt Control Register (INC1) to output the physical interrupt of the previously defined Tilt Position function. This value will create an active high and latched interrupt.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x30  |

- Write 0x01 to Interrupt Control Register 4 (INC4) to set the Tilt Position interrupt (TPI1) to be reported on physical interrupt pin INT1.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC4          | 0x25    | 0x01  |

- Write 0xC1 to Control Register 1 (CNTL1) to set the accelerometer in operating mode, high performance (full power), G-range to ±8g, and enable the Tilt Position function.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xC1  |

- Monitor the physical interrupt INT1 of the accelerometer. If changes in the tilt position satisfies the criteria previously established, then there should be a positive latched interrupt present. Also, the interrupt would be reflected in bit 4 of STATUS\_REG (INT bit), bit 0 of INS2 (TPS bit), and Current Tilt Position register TSCP as well as Previous Tilt Position register TSPP.

- Read Interrupt Latch Release (INT\_REL) register to unlatch (clear) the output interrupt created by the Tilt Position function. The read value is dummy.

| Register Name | Address | Value |

|---------------|---------|-------|

| INT_REL       | 0x1A    | N/A   |

### 3.6.2. Face Detect Position

- As was noted above, the current orientation of the sensor can be read from TSCP register at any time. Assuming tilt detection was not changed from its default setting (detect positive and negative directions of all three axes (+x, -x, +y, -y, +z, -z)), one of the bits in TSCP register will be set to 1 to indicate the current orientation of the sensor.

# 3.7. Activate Tap/Double Tap Engine

Write 0x00 to Control Register 1 (CNTL1) to set the accelerometer in stand-by mode.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

- Write 0x3F to Interrupt Control 3 register (INC3) to enable tap/double tap from positive and negative directions of all three axes (+x, -x, +y, -y, +z, -z). This step is optional as this is also a default setting.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC3          | 0x24    | 0x3F  |

- Write 0xA8 to Control 3 register (CNTL3) to set the output data rate for the Directional Tap function to 400Hz. *This step is optional as this is also a default setting.*

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL3         | 0x1D    | 0xA8  |

- Write 0x03 to Tap / Double-Tap Register Control register (TDTRC) to enable interrupt on single tap <u>and</u> double tap. This step is optional as this is also a default setting. *This setting can be adjusted as needed.*

| Register Name | Address | Value |

|---------------|---------|-------|

| TDTRC         | 0x2A    | 0x03  |

- Write 0x78 to Tap / Double-Tap Counter register (TDTC) to set the counter to 0.3 sec. The TDTC counts starts at the beginning of the fist tap and it represents the minimum time separation between the first tap and the second tap in a double tap event. More specifically, the second tap event must end outside of the TDTC. This step is optional as this is also a default setting. This setting can be adjusted as needed.

| Register Name | Address | Value |

|---------------|---------|-------|

| TDTC          | 0x2B    | 0x78  |

- Write 0x33 (51d) to Tap Threshold High register (TTH). This register represents the 8-bit jerk high threshold to determine if a tap is detected. Though this is an 8-bit register, the register value is internally multiplied by two to set the high threshold. This multiplication results in a range of 0d to 510d with a resolution of two counts. The Performance Index (PI) is the jerk signal that is expected to be less than this threshold, but greater than the TTL threshold during single and double tap events. This step is optional as this is also a default setting. This setting can be adjusted as needed.

| Register Name | Address | Value |

|---------------|---------|-------|

| TTH           | 0x2C    | 0x33  |

Write 0x07 (7d) to Tap Threshold Low register (TTL). This register represents the 8-bit (0d–255d) jerk low threshold to determine if a tap is detected. The Performance Index (PI) is the jerk signal that is expected to be greater than this threshold and less than the TTH threshold during single and double tap events. This step is optional as this is also a default setting. This setting can be adjusted as needed.

| Register Name | Address | Value |

|---------------|---------|-------|

| TTL           | 0x2D    | 0x07  |

Write 0xA2 (162d) to set the FTD counter register to 0.005 seconds. This register contains counter information for the detection of <u>any</u> tap event. A tap event must be above the performance index threshold for at least the low limit (FTDL0 – FTDL2) and no more than the high limit (FTDH0 – FTDH4). This step is optional as this is also a default setting. This setting can be adjusted as needed.

| Register Name | Address | Value |

|---------------|---------|-------|

| FTD           | 0x2E    | 0xA2  |

- Write 0x24 (36d) to set the STD counter register to 0.09 seconds. This register contains counter information for the detection of a <u>double</u> tap event. This register sets the total amount of time that the two taps in a double tap event can be above the PI threshold (TTL). *This step is optional as this is also a default setting.* This setting can be adjusted as needed.

| Register Name | Address | Value |

|---------------|---------|-------|

| STD           | 0x2F    | 0x24  |

- Write 0x28 (40d) to set the TLT counter register to 0.1 seconds. This register contains counter information for the detection of a tap event. This register sets the total amount of time that the tap algorithm will count samples that are above the PI threshold (TTL) during a potential tap event. It is used during both single and double tap events. However, reporting of single taps on the physical interrupt pin INT1 or INT2 will occur at the end of the TWS. This step is optional as this is also a default setting. This setting can be adjusted as needed.

| Register Name | Address | Value |

|---------------|---------|-------|

| TLT           | 0x30    | 0x28  |

- Write 0xA0 (160d) to set the TWS counter register to 0.4 seconds. This register contains counter information for the detection of single and double taps. This counter defines the time window for the entire tap event, single or double, to occur. Reporting of single taps on the physical interrupt pin INT1 or INT2 will occur at the end of this tap window. *This step is optional as this is also a default setting.* This setting can be adjusted as needed.

| Register Name | Address | Value |

|---------------|---------|-------|

| TWS           | 0x31    | 0xA0  |

- Write 0x30 to Interrupt Control Register (INC1) to output the physical interrupt of the previously defined Tap/Double-Tap function. This value will create an active high and latched interrupt.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x30  |

- Write 0x04 to Interrupt Control Register 4 (INC4) to set the Tap/Double-Tap interrupt (TDTI) to be reported on physical interrupt pin INT1.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC4          | 0x25    | 0x04  |

- Write 0xC4 to Control Register 1 (CNTL1) to set the accelerometer in operating mode, high performance (full power), G-range to ±8g, and enable the Directional Tap function.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xC4  |

- Monitor the physical interrupt INT1 of the accelerometer, if the acceleration input profile satisfies the criteria previously established for Tap/Double-Tap, then there should be a positive latched interrupt present. Also, the interrupt would be reflected in bit 4 of STATUS\_REG (INT bit), and bit 3 and bit 2 of INS2 registers. To distinguish between a single and double-tap events, monitor INS2 register bits <TDTS1:TDTS0>. TDTS1 bit3 would be set for Double-tap event, and TDTS0 bit2 for Single-tap event. Also, INS1 register can be monitored to identify the direction the tap came from.

- Read Interrupt Latch Release (INT\_REL) register to unlatch (clear) the output interrupt created by the Tap/Double-Tap detection function. The read value is dummy.

| Register Name | Address | Value |

|---------------|---------|-------|

| INT_REL       | 0x1A    | N/A   |

# 3.8. Activate Free-fall Engine

Write 0x00 to Control Register 1 (CNTL1) to set the accelerometer in stand-by mode.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0x00  |

- Write 0x80 to Free-Fall Control Register (FFCNTL) to enable Free fall engine, to set Free-fall interrupt latch control, count up/down debounce methodology, and the Output Data Rate (ODR) to 12.5Hz (Default).

| Register Name | Address | Value |

|---------------|---------|-------|

| FFCNTL        | 0x34    | 0x80  |

- Write 0x08 to Free-Fall Threshold Register (FFTH) to set the Free-fall threshold to 0.5g based on the following equation:

FFTH [counts] \* 0.0625 [g/counts] = Free-fall Threshold [g]

8 [counts] \* 0.0625 [g/count] = 0.5 [g]

| Register Name | Address | Value |

|---------------|---------|-------|

| FFTH          | 0x32    | 0x08  |

- Write 0x04 to Free-Fall Counter Register (FFC) to set the Free-fall delay detection to 0.320 sec. Note that the period of the free-fall counter is a function of Free-fall ODR set by <OFFI2:OFF0> bits in FFCTNL register. The following equation can be used:

FFC [counts] / Free-Fall ODR [Hz] = Free-fall delay [sec]

4 [counts] / 12.5 [Hz] = 0.320 [sec]

| Register Name | Address | Value |

|---------------|---------|-------|

| FFC           | 0x33    | 0x04  |

- Write 0x30 to Interrupt Control Register (INC1) to output the physical interrupt of the previously defined Free-fall detect function. This value will create an active high and latched interrupt.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC1          | 0x22    | 0x30  |

- Write 0x80 to Interrupt Control Register 4 (INC4) to set the Free-fall interrupt (FFI) to be reported on physical interrupt pin INT1.

| Register Name | Address | Value |

|---------------|---------|-------|

| INC4          | 0x25    | 0x80  |

- Write 0xC0 to Control Register 1 (CNTL1) to set the accelerometer in operating mode, high performance (full power), and G-range to ±8g.

| Register Name | Address | Value |

|---------------|---------|-------|

| CNTL1         | 0x1B    | 0xC0  |

- Monitor the physical interrupt INT1 of the accelerometer, if the acceleration input profile satisfies the criteria previously established for the 0.5g free-fall detect threshold level in both positive and negative directions of the X, Y, Z axis for more than 0.320 second, then there should be a positive latched interrupt present. Free-fall events will now be reflected in bit 4 of STATUS\_REG (INT bit), and bit 7 of INS2 registers,

- Read Interrupt Latch Release (INT\_REL) register to unlatch (clear) the output interrupt created by the free-fall detection function. The read value is dummy.

| Register Name | Address | Value |

|---------------|---------|-------|

| INT_REL       | 0x1A    | N/A   |

# 4. Timing Requirements

There are several timing requirements that developers should keep in mind when working with the KX126 accelerometer:

<u>I<sup>2</sup>C Clock</u> - The I<sup>2</sup>C Clock can support Fast Mode up to **400 KHz** and High Speed mode up to **3.4 MHz**.

<u>SPI Clock</u> - The SPI Clock can support up to **10 MHz**.

<u>Enable to Valid Outputs (Start-Up Time)</u> - After the part is enabled (PC1 bit in Control Register 1 is asserted), it takes from **2 ms** to **1300 ms** depending on the ODR and Power Mode setting before the acceleration outputs are valid. (See the relevant Product Specification for details)

<u>Power-Up Time (Time from VDD and IO\_VDD valid to device boot completion)</u> - After a Power-up, the part takes between **20 ms** to **50 ms** before it is ready for communication.

<u>Software Reset Delay</u> - After a Software Reset, the part takes **2 ms** before it is ready for communication.

<u>Standby to Operation Delay</u> - Please allow 1.5/ODR delay time when transitioning from stand-by PC1 = 0 to operating mode PC1 = 1 to allow new settings to load.

# 5. Interrupt Configuration

The physical interrupt has 6 possible configurations, based on two states for each of the three customizable variables located in Interrupt Control Register 1:

# <u>Latched/Pulsed (IEL – bit 3 – 0x08)</u>

- 0 Latched mode When an interrupt is triggered, it will remain active on the pin until cleared.

- 1 Pulse mode When an interrupt is triggered, it will cause a short (~50µs) pulse on the pin and clear itself.

#### Polarity (IEA – bit 4 - 0x10)

- 0 Active Low The interrupt pin will normally be HIGH, but will transition to LOW when an interrupt is triggered.

- 1 Active High The interrupt pin will normally be LOW, but will transition to HIGH when an interrupt is triggered.

#### Enable/Disable (IEN – bit 5 - 0x20)

- 0 Disabled Interrupt conditions will not be reflected on the physical interrupt pin.

- 1 Enabled Interrupt conditions will be reflected on the physical interrupt pin.

# 5.1. A Few Interrupt Tips

# Read the Interrupt Release Register to Clear

In latched mode, the INT\_REL register must be read in order to clear the physical interrupt pin. This will also clear the Interrupt Source Registers and the INT bit (0x10) in the Status Register.

# Microcontroller/GPIO Interrupt Handling -

GPIO configuration is based solely on the connected hardware. The accelerometers in this family can be configured to issue interrupts depending on how the GPIO is programmed to catch them (if this is not the case, please contact your Kionix Sales Representative). Generally, when an interrupt is triggered, the developer should take the following steps:

- 1- Disable GPIO interrupt

- 2- Clear GPIO interrupt and generate desired functionality

- 3- Enable GPIO interrupt

These steps should be taken without calling any digital communication transactions if done in an interrupt context, because the operating system or kernel will not allow busy-waiting on an I/O operation during an interrupt service routine.

<u>Interrupt Polling</u> - If physical interrupts are not used, a polling mechanism can be devised, which checks the INT bit in STATUS\_REG. This mechanism should then look at INS2 to determine which engine caused the interrupt and what steps should be taken before clearing the interrupt source information by reading the INT\_REL register.

# 6. Troubleshooting

#### All Interrupt Issues

- Make sure the accelerometer is configured to issue interrupt signals in the way that your GPIO is programmed to handle them.

- An oscilloscope on the physical interrupt pin can be a valuable tool to confirm physical interrupt operation.

- Double check the Tilt Position State Mask bits in Control Register 2 (Tilt Position Function), the axis mask bits in Interrupt Control Register 2 (Wake-up Function), and/or the Tap/Double-Tap Mask bits in Interrupt Control Register 3 (Tap/Double-Tap Function), and Free Fall Threshold value in Free Fall Threshold Register (Free Fall Detect Function)

- The Tilt Timer, WUF Timer, and TDT Timer(s) are based on their respective Output Data Rates, so make sure the correct cycle time is used when calculating the expected timer length (please refer to the specific product specification).

#### Tilt Interrupt Not Working

- Make sure that the Tilt Position engine is enabled (TPE bit in Control Register 1).

- Try shortening the timer requirements and make sure the next state transition does not occur until after the expiration of the Tilt Timer.

- Try increasing the Tilt Angle to ensure that the engine can see the transition between the X and Y axes and the Z axis (this should not be necessary if using the default value for Tilt Angle, but it's worth considering if problems continue).

#### WUF (Wake Up Function) and or BTS (Back-to-Sleep) Interrupts Are Not Working

- Make sure that the Wake-Up Function is enabled (WUFE bit in Control Register 4).

- Make sure that the Back-to-Sleep engine is enabled (BTSE bit in Control Register 4).

- If Back-to-Sleep function is not used (BTSE bit in Control Register 3 left at 0), the *sleep* mode should be forced during the initial setup and after each Wake-up interrupt has fired through setting MAN\_SLEEP bit to 1 in Control Register 5 (CNTL5). This will also clear WAKE bit in the STAT register to indicate the wake state is no longer valid.

- Make sure the interrupt release register INT\_REL is read to clear the latched interrupt if was set previously, to clear WUFS and/or BTS bits in Interrupt Status 3 (INS3) registers.

- Try altering the threshold requirements to achieve desired operation. If the part is waking up too easily, try increasing the threshold. If the interrupt is not firing at all, the threshold may be set too high.

- Try shortening the timer requirements, and make sure the acceleration on an unmasked axis is above the threshold until the expiration of the WUF Timer.

#### TDT (Tap/Double-Tap) Interrupt Not Working

- Make sure that the TDT engine is enabled (TDTE bit in Control Register 1).

- Try altering the threshold requirements to achieve desired operation. If the part is generating interrupts too often, perhaps due to a large noise floor created by excessive environmental vibrations, try increasing the performance index low threshold (TTL) and/or reducing the performance index high threshold (TTH). If the interrupt is not firing at all, perhaps the low threshold may be set too high, or the high threshold may be set too low.

- There are many timers in this engine which must work together closely, so for standard operation if one timer is changed the other timers may need to be changed proportionally.

# Free fall Detect Interrupt Not Working

- Make sure the Free fall engine is enabled (FFIE bit in Free Fall Control Register FFCNTL)

- Try adjusting the threshold requirements to achieve desired operation by adjusting the threshold value in the FFTH register. If the part is generating interrupts two often, try increasing the delay/debounce time in the FFC register. If the interrupt is not firing at all, perhaps the threshold is set too high.

#### 7. Accelerometer Placement and Orientation

<u>Placement</u> – It is important to note that the placement of the accelerometer within the target device can have a significant effect on tap/double-tap direction resolution. If tap detection is desired, the part should be placed as far away from the edges of the device housing as possible, with the ideal location being at the target device's center of mass.

<u>Orientation</u> – While it is recommended to align the accelerometer's axes with those of the target device, it will sometimes be desirable or necessary to alter the part's orientation with respect to the device housing. Rotating about the Z axis at intervals of 90 degrees or about the X or Y axes at intervals of 180 degrees should not impact functionality. However, it is highly recommended that the device is not rotated 90 or 270 degrees about the X or Y axes. Due to the asymmetrical nature of the tilt position function, altering the orientation of the Z axis in this manner can cause incorrect screen rotation direction resolution.

# 8. The Kionix Advantage

Kionix technology provides for X, Y, and Z-axis sensing on a single, silicon chip. One accelerometer can be used to enable a variety of simultaneous features including, but not limited to:

Hard Disk Drive protection

Vibration analysis

Tilt screen navigation

Sports modeling

Theft, man-down, accident alarm

Image stability, screen orientation & scrolling

Computer pointer

Navigation, mapping

Game playing

Automatic sleep mode

Step counting (pedometer)

# 9. Theory of Operation

Kionix MEMS linear tri-axis accelerometers function on the principle of differential capacitance arising from the acceleration induced motion. Acceleration causes displacement of a silicon structure resulting in a change in capacitance. A signal-conditioning CMOS technology ASIC detects and transforms changes in capacitance, which is proportional to acceleration, into an analog output voltage that is sent through an analog-to-digital converter. The acceleration data may be accessed through the output data registers by the micro-controller for use in various applications.

For product summaries, specifications, and schematics, please refer to the Kionix MEMS accelerometer product catalog at <a href="http://www.kionix.com/parametric/Accelerometers">http://www.kionix.com/parametric/Accelerometers</a>