#### Dear customer

LAPIS Semiconductor Co., Ltd. ("LAPIS Semiconductor"), on the 1<sup>st</sup> day of October, 2020, implemented the incorporation-type company split (shinsetsu-bunkatsu) in which LAPIS established a new company, LAPIS Technology Co., Ltd. ("LAPIS Technology") and LAPIS Technology succeeded LAPIS Semiconductor's LSI business.

Therefore, all references to "LAPIS Semiconductor Co., Ltd.", "LAPIS Semiconductor" and/or "LAPIS" in this document shall be replaced with "LAPIS Technology Co., Ltd."

Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

LAPIS Technology Co., Ltd. October 1, 2020

64k(8,192-Word × 8-Bit) FeRAM (Ferroelectric Random Access Memory) SPI

#### **GENERAL DESCRIPTION**

The MR45V064B is a nonvolatile 8,192-word x 8-bit ferroelectric random access memory (FeRAM) developed in the ferroelectric process and silicon-gate CMOS technology. The MR45V064B is accessed using Serial Peripheral Interface.Unlike SRAMs, this device, whose cells are nonvolatile, eliminates battery backup required to hold data. This device has no mechanisms of erasing and programming memory cells and blocks, such as those used for various EEPROMs. Therefore, the write cycle time can be equal to the read cycle time and the power consumption during a write can be reduced significantly.

> 40MHz 10<sup>12</sup> cycles/bit

The MR45V064B can be used in various applications, because the device is guaranteed for the write/read tolerance of  $10^{12}$  cycles per bit and the rewrite count can be extended significantly.

#### FEATURES

- 8,192-word × 8-bit configuration (Serial Peripheral Interface : SPI)

- A single 1.8V to 3.6V (3.3 V typ) power supply

- Operating frequency:

- Read/write tolerance

- Data retention

- .

- Guaranteed operating temperature range

- 10 years -40 to 85°C (Extended temperature version)

- Package options:

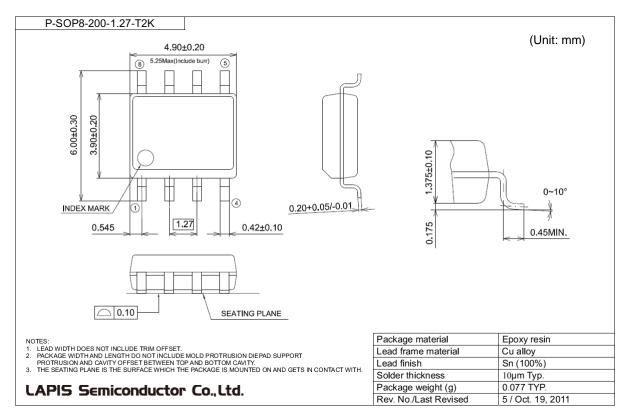

- 8-pin plastic SOP (P-SOP8-200-1.27-T2K)

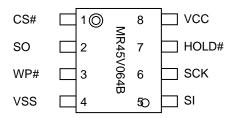

#### **PIN CONFIGURATION**

#### 8-pin plastic SOP

Note:

Signal names that end with # indicate that the signals are negative-true logic.

#### **PIN DESCRIPTIONS**

| Pin Name                          | Description                                                                                                                                                                                                                                                                     |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#                               | Chip Select (input, negative logic)<br>Latches an address by low input, activates the FeRAM, and enables a read or write<br>operation.                                                                                                                                          |

| WP#                               | <ul><li>Write Protect( input , negative logic )</li><li>Write Protect pin controls write-operation to the status-register(BP0,BP1). This pin should be fixed low or high in write-operations.</li></ul>                                                                         |

| HOLD#                             | HOLD( input , negative logic )<br>Hold pin is used when the serial-communication suspended without disable the chip<br>select. When HOLD# is low ,the serial-output is in High-Z status and<br>serial-input/serial-clock are "Don't Care". CS# should be low in hold operation. |

| SCK                               | Serial Clock<br>Serial Clock is the clock input pin for setting for serial data timing. Inputs are latched on<br>the rising edge and output occur on the falling edge.                                                                                                          |

| SI                                | Serial input<br>SI pins are serial input pins for Operation-code , addresses ,and data-inputs .                                                                                                                                                                                 |

| SO                                | Serial output<br>SO pins are serial output pins.                                                                                                                                                                                                                                |

| V <sub>CC</sub> , V <sub>SS</sub> | Power supply Apply the specified voltage to $V_{CC}$ . Connect $V_{SS}$ to ground.                                                                                                                                                                                              |

FEDR45V064B-01

MR45V064B

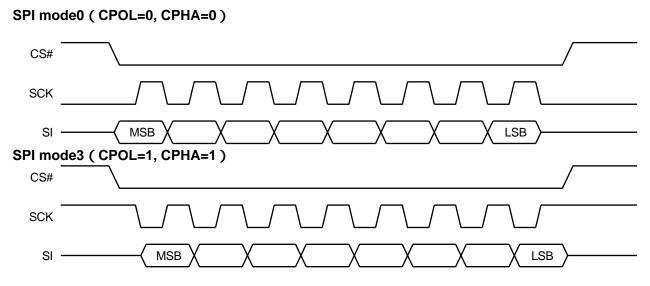

#### SPIMODE

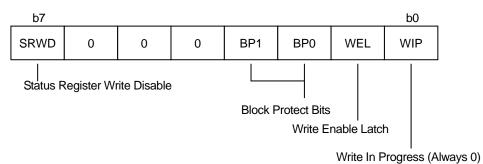

#### STATUS REGISTER

| Name    | Function                                                                                                                                                        |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| WIP     | Fixed to 0.                                                                                                                                                     |  |  |  |  |

| WEL     | Write Enable Latch. This indicates internal WEL condition.                                                                                                      |  |  |  |  |

| BP0,BP1 | Block Protect: These bits can be changed protect area.                                                                                                          |  |  |  |  |

|         | This is the software protect.                                                                                                                                   |  |  |  |  |

| SRWD    | Status Register Write Disable (SRWD): SRWD controls the effect of the hardware WP# pin. This device will be in hardware-protect by combination of SRWD and WP#. |  |  |  |  |

| 0       | Fixed to 0.                                                                                                                                                     |  |  |  |  |

#### **OPERATION-CODE**

Operation codes are listed in the table below. If the device receives invalid operation code, the device will be diselected.

| Instruction | Description                 | Instruction format |

|-------------|-----------------------------|--------------------|

| WREN        | Write Enable                | 0000 0110          |

| WRDI        | Write Disable               | 0000 0100          |

| RDSR        | Read Status Register        | 0000 0101          |

| WRSR        | Write Status Register       | 0000 0001          |

| READ        | Read from Memory Array      | 0000 0011          |

| WRITE       | Write to Memory Array       | 0000 0010          |

| FSTRD       | Fast Read from Memory Array | 0000 1011          |

| RDID        | Read device ID              | 1001 1111          |

#### COMMANDS

#### WREN (Write Enable)

It is necessary to set Write Enable Latch (WEL) bit before write-operation (WRITE and WRSR). WREN command sets WEL bit.

| CS#    |                              |

|--------|------------------------------|

| WP#    | Fixed "H"                    |

| SCK    |                              |

| SI     |                              |

| SO     | High-Z                       |

| WRDI   | (Write Disable)              |

| WRDI o | command resets WEL bit.      |

| CS#    |                              |

| WP#    | Fixed "H"<br>0 1 2 3 4 5 6 7 |

| SCK    |                              |

| SI     |                              |

| SO     | <br>High-Z                   |

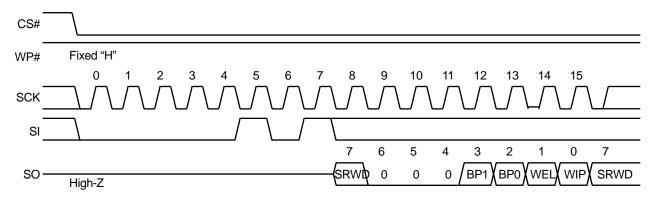

#### RDSR (READ Status Register)

The RDSR command allows to read data of status register.

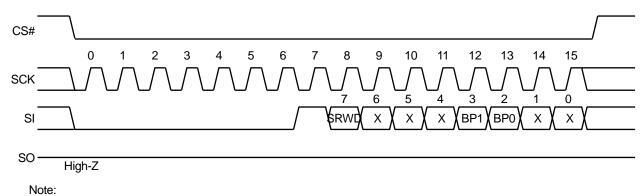

#### WRSR (WRITE Status Register)

WRSR command allows to write data to status register(SRWD,BP0,BP1). It is necessary to set Write Enable Latch (WEL) bit by WREN command before executing WRSR.

WP#=Fix "H"

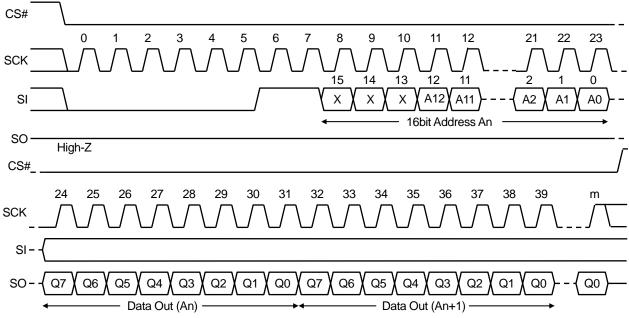

#### READ (Read from Memory Array)

READ command can be valid when CS# goes "L", then the op-code and 16bit-adresses are inputted to serial input"SI". The inputted adresses are loaded to internal register, then the data from corresponded address is output at serial-output "SO". If CS# will keep "L", the internal adress will be incressed automatically after 8 clocks and will output the data from new-address. When it reaches the most significant adress, the adress counter rolls over tostarting adress, and reading cycle can be continued infinitely.

Note : WP# = fixed "H"

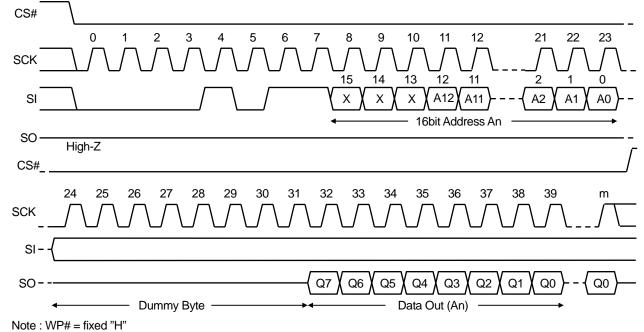

#### FSTRD (Fast Read from Memory Array)

FSTRD command can be valid when CS# goes "L", then the op-code and 16bit-adresses are inputted to serial input "SI". After 8bits for dummy byte, the data from corresponded address is output at serial-output "SO".

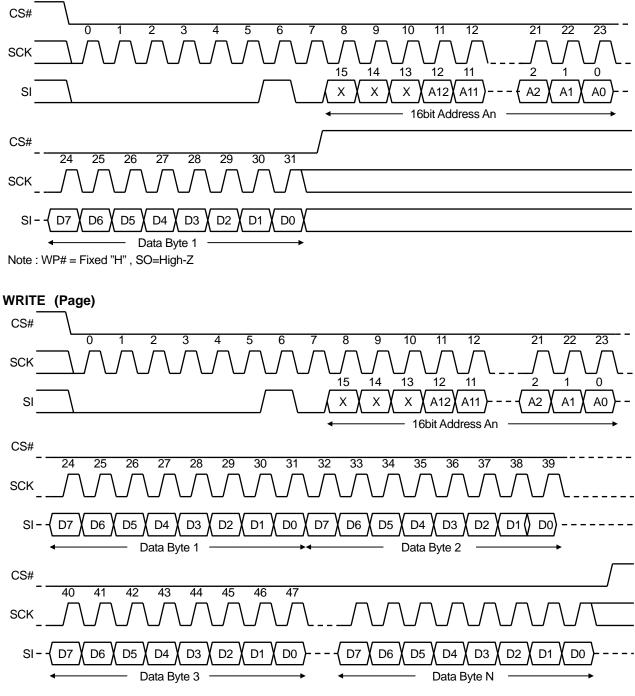

#### WRITE (Write to Memory Array)

Write command can be valid when CS# goes "L",then the op-code and 16bit-adresses are inputted to serial input"SI". Writing is terminated when CS# goes high after data-input. If CS# will keep "L",the internal adress will be increased automatically.When it reaches the most significant adress,the adress counter rolls over to starting adress 0000h,and writing cycle(overwriting) can be continued infinitely.

#### WRITE (1Byte)

Note : WP# = Fixed "H" , SO=High-Z

#### WRITE PROTECTION

Writing protection block is shown as follows:

#### Protect Block size

| Block Protect BIT |     | Protected Block | Protected Address Area |                        |  |

|-------------------|-----|-----------------|------------------------|------------------------|--|

|                   | BP1 | BP0             | PTOLECIEU DIOCK        | FIDIECIED ADDIESS AIEa |  |

| 0                 |     | 0               | None                   | None                   |  |

| 0                 |     | 1               | Upper 1/4 block        | 1800h – 1FFFh          |  |

| 1                 |     | 0               | Upper 1/2 block        | 1000h – 1FFFh          |  |

| 1                 |     | 1               | All                    | 0000h – 1FFFh          |  |

#### Writing Protect

|     |      |                                 | Writing protection status                                          | Protection status in memory |                    |  |

|-----|------|---------------------------------|--------------------------------------------------------------------|-----------------------------|--------------------|--|

| WP# | SRWD | mode                            | in status register                                                 | Protected blocks            | Unprotected blocks |  |

| 1   | 0    | 0.1                             | Status register is                                                 |                             |                    |  |

| 0   | 0    | Software<br>protection<br>(SPM) | unprotected when<br>WEL-bit is set by WREN<br>command, BP0 and BP1 | Protected                   | Unprotected        |  |

| 1   | 1    |                                 | are unprotected.                                                   |                             |                    |  |

| 0   | 1    | Hardware<br>protection<br>(HPM) | Status register is protected. BP0 and BP1 are protected.           | Protected                   | Unprotected        |  |

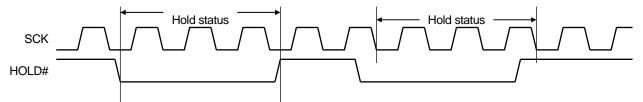

#### HOLD

Hold status is used for suspending serial comunication without disable the chip. SO becomes "High-Z" and SI is "Don't care" during the hold status. It is necessary to keep CS#=L in hold status.

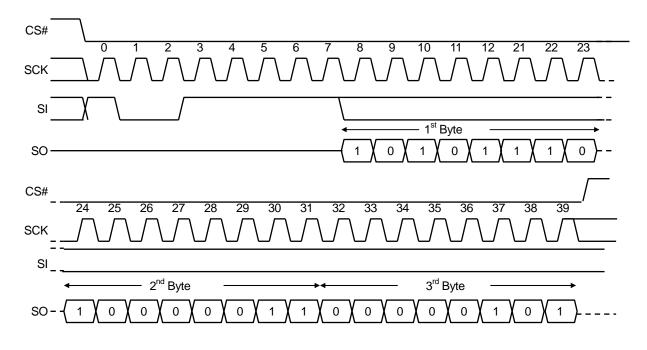

#### **RDID ( Read device ID)**

RDID command can be valid when CS# goes "L", then the op-code are inputted to serial input"SI". Then 3bytes of device ID is output at serial-output "SO".

| Manufacture id ( LAPIS ) | device type (MR45V064B) |                      |  |

|--------------------------|-------------------------|----------------------|--|

| 1 <sup>st</sup> Byte     | 2 <sup>nd</sup> Byte    | 3 <sup>rd</sup> Byte |  |

| AEh                      | 83h                     | 05h                  |  |

Note : WP# = Fixed "H"

#### ELECTRICAL CHARACTERISTICS

#### ABSOLUTE MAXIMUM RATINGS

The application of stress (voltage, current, or temperature) that exceeds the absolute maximum rating may damage the device. Therefore, do not allow actual characteristics to exceed any one parameter ratings

#### **PIN VOLTAGES**

| Deremeter                          | Symbol                               | Rat  | 1 1 1 1 1 1           |      |

|------------------------------------|--------------------------------------|------|-----------------------|------|

| Parameter                          | Symbol                               | Min. | Max.                  | Unit |

| Pin Voltage (Input Signal)         | V <sub>IN</sub>                      | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Pin Voltage (Input/Output Voltage) | V <sub>INQ</sub> , V <sub>OUTQ</sub> | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Power Supply Voltage               | V <sub>CC</sub>                      | -0.5 | 4.0                   | V    |

#### **TEMPERATURE RANGE**

| Parameter                                               | Symbol | Symbol Rating |      | Unit | Note |

|---------------------------------------------------------|--------|---------------|------|------|------|

| Parameter                                               | Symbol | Min.          | Max. | Unit | Note |

| Storage Temperature<br>(Extended Temperature Version)   | Tstg   | -55           | 125  | °C   |      |

| Operating Temperature<br>(Extended Temperature Version) | Topr   | -40           | 85   | °C   |      |

#### OTHERS

| Parameter         | Symbol         | Rating  | Note    |

|-------------------|----------------|---------|---------|

| Power Dissipation | P <sub>D</sub> | 1,000mW | Ta=25°C |

#### **RECOMMENDED OPERATING CONDITIONS**

#### POWER SUPPLY VOLTAGE

|                      |                 |      |      |      | [V]  |

|----------------------|-----------------|------|------|------|------|

| Parameter            | Symbol          | Min. | Тур. | Max. | Note |

| Power Supply Voltage | V <sub>CC</sub> | 1.8  | 3.3  | 3.6  |      |

| Ground Voltage       | V <sub>SS</sub> | 0    | 0    | 0    |      |

#### DC INPUT VOLTAGE

|                    |                 |                       |                       | [V]  |

|--------------------|-----------------|-----------------------|-----------------------|------|

| Parameter          | Symbol          | Min.                  | Max.                  | Note |

| Input High Voltage | V <sub>IH</sub> | V <sub>CC</sub> x 0.7 | V <sub>CC</sub> +0.3  |      |

| Input Low Voltage  | V <sub>IL</sub> | -0.3                  | V <sub>CC</sub> x 0.3 |      |

#### OVERSHOOT/UNDERSHOOT TOLERANCE

| Parameter | Symbol         | Pulse Width | Peak                  |  |

|-----------|----------------|-------------|-----------------------|--|

| "H" input | VIH OVERSHOOT  | ≤ 20ns      | V <sub>CC</sub> +1.0V |  |

| "L" input | VIL UNDERSHOOT | ≤ 20ns      | – 1.0V                |  |

#### **DC CHARACTERISTICS**

#### DC INPUT/OUTPUT CHARACTERISTICS

| Parameter                 | Symbol          | Condition             | Min.                  | Max.                  | Unit | Note                  |

|---------------------------|-----------------|-----------------------|-----------------------|-----------------------|------|-----------------------|

| Output High Voltage       | V               | l2m∧                  | V <sub>CC</sub> ×0.85 | _                     | V    | V <sub>CC</sub> 2.0V  |

| Output High Voltage       | V <sub>OH</sub> | I <sub>OH</sub> =—2mA | V <sub>CC</sub> ×0.80 | _                     | V    | V <sub>CC</sub> <2.0V |

| Output Low Voltage        | V <sub>OL</sub> | I <sub>OL</sub> =2mA  | —                     | V <sub>CC</sub> ×0.15 | V    |                       |

| Input Leakage Current     | Ι <sub>LI</sub> | _                     | -10                   | 10                    | μA   |                       |

| Output Leakage<br>Current | I <sub>LO</sub> | _                     | -10                   | 10                    | μA   |                       |

#### POWER SUPPLY CURRENT

V<sub>CC</sub>=Max.to Min, Ta=Topr

| Parameter                           | Symbol           | Condition                                                                           | Max. | Unit | Note |

|-------------------------------------|------------------|-------------------------------------------------------------------------------------|------|------|------|

| Power Supply Current (Standby)      | I <sub>CCS</sub> | $V_{IN}$ =0.2V or $V_{CC}$ -0.2V                                                    | 10   | μA   |      |

| Power Supply Current<br>(Operating) | I <sub>CCA</sub> | V <sub>IN</sub> =0.2V or V <sub>CC</sub> -0.2V,<br>SCK=40MHz, I <sub>OUT</sub> =0mA | 3    | mA   |      |

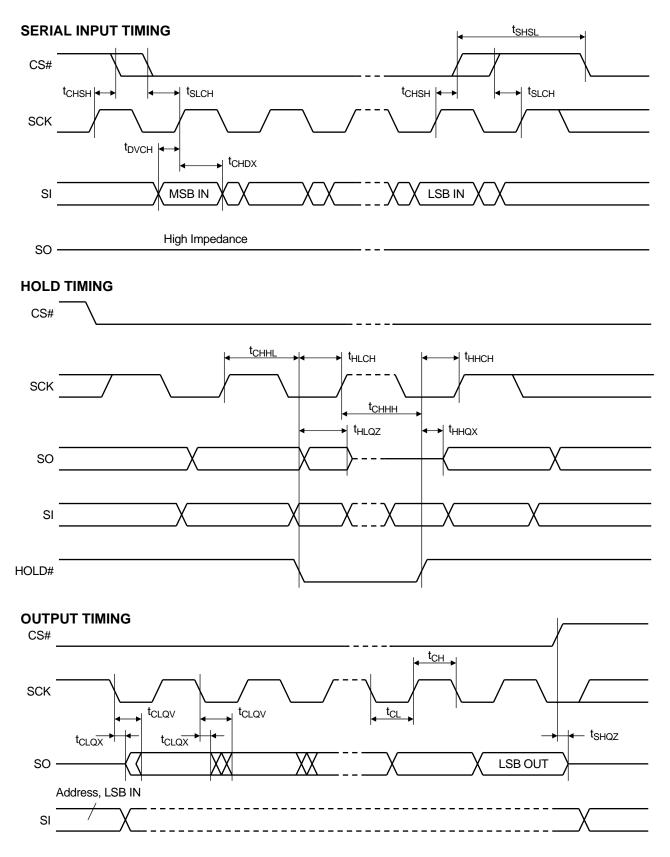

### AC CHARACTERISTICS (Read Cycle)

V<sub>CC</sub>=Max. to Min., Ta=Topr.

|                                             |                     | MR45V064B |      |      |                       |

|---------------------------------------------|---------------------|-----------|------|------|-----------------------|

| Parameter                                   | Symbol              |           |      | Unit | Note                  |

|                                             | ,                   | Min.      | Max. |      |                       |

| Clock frequency                             | f <sub>C</sub>      | D.C.      | 40   | MHz  |                       |

| CS# setup time                              | t <sub>SLCH</sub>   | 10        | —    | ns   |                       |

| CS# De-select time                          | t <sub>SHSL</sub>   | 40        | —    | ns   |                       |

| CS# hold time                               | t <sub>CHSH</sub>   | 10        | —    | ns   |                       |

| SCK High time                               | t <sub>CH</sub>     | 11        | —    | ns   | 1                     |

| SCK Low time                                | t <sub>CL</sub>     | 11        | _    | ns   | 1                     |

| Data Setup time                             | t <sub>DVCH</sub>   | 5         | —    | ns   |                       |

| Data Hold time                              | t <sub>CHDX</sub>   | 5         | —    | ns   |                       |

| SCK Low Hold time after HOLD# inactive      | t <sub>HHCH</sub>   | 10        | —    | ns   |                       |

| SCK Low Hold time after HOLD# active        | t <sub>HLCH</sub>   | 10        | —    | ns   |                       |

| SCK High Setup time before HOLD# active     | t <sub>CHHL</sub>   | 10        | —    | ns   |                       |

| SCK High Setup time before HOLD# inactive   | t <sub>CHHH</sub>   | 10        | —    | ns   |                       |

| Output disable time                         | t <sub>SHQZ</sub>   | _         | 12   | ns   | 2                     |

|                                             | t <sub>CLQV</sub> — | _         | 9    | ns   | V <sub>CC</sub> ≧2.7V |

| SCK Low to Output Valid time                |                     | _         | 10   | ns   | V <sub>CC</sub> <2.7V |

| Output Hold time                            | t <sub>CLQX</sub>   | 0         | _    | ns   |                       |

| HOLD# High to Output Low<br>impedance time  | t <sub>HHQX</sub>   | _         | 20   | ns   | 2                     |

| HOLD# High to Output High<br>impedance time | t <sub>HLQZ</sub>   | —         | 20   | ns   | 2                     |

Note:  $1. t_{CH} + t_{CL} \ge 1/f_C$

2. sample value

FEDR45V064B-01

MR45V064B

#### TIMING DIAGRAMS

MR45V064B

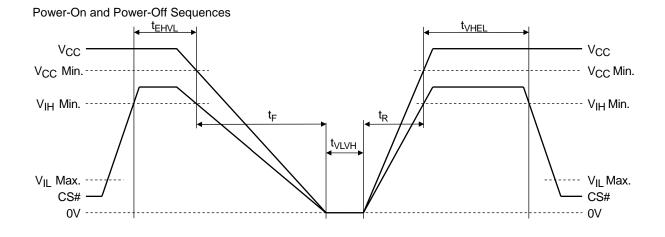

#### **POWER-ON and POWER-OFF CHARACTERISTICS**

| POWER-ON and POWER-OFF CHARACTERISTICS |                   |            |           |             |             |  |  |

|----------------------------------------|-------------------|------------|-----------|-------------|-------------|--|--|

|                                        |                   | (Under red | commended | d operating | conditions) |  |  |

| Parameter                              | Symbol            | Min.       | Max.      | Unit        | Note        |  |  |

| Power-On CS# High Hold Time            | t <sub>VHEL</sub> | 100        | _         | ns          | 1, 2        |  |  |

| Power-Off CS# High Hold Time           | t <sub>EHVL</sub> | 0          |           | ns          | 1           |  |  |

| Power-On Interval Time                 | t <sub>VLVH</sub> | 0          |           | μs          | 2           |  |  |

| Power-On time                          | tR                | 30         |           | μs/V        |             |  |  |

| Power-Off time                         | tF                | 30         | _         | μs/V        |             |  |  |

Notes:

1. To prevent an erroneous operation, be sure to maintain CS#="H", and set the FeRAM in an inactive state (standby mode) before and after power-on and power-off.

2. Powering on at the intermediate voltage level will cause an erroneous operation; thus, be sure to power up from 0 V.

3. Enter all signals at the same time as power-on or enter all signals after power-on.

#### **READ/WRITE CYCLES and DATA RETENTION**

| READ/WRITE GTGLES and DATA RETENTION |                  |      |       |      |  |  |  |

|--------------------------------------|------------------|------|-------|------|--|--|--|

| (Under recommended operating conditi |                  |      |       |      |  |  |  |

| Parameter                            | Min.             | Max. | Unit  | Note |  |  |  |

| Read/Write Cycle                     | 10 <sup>12</sup> | _    | Cycle |      |  |  |  |

| Data Retention                       | 10               | —    | Year  |      |  |  |  |

#### CAPACITANCE

| Signal                   | Symbol           | Min. | Max. | Unit | Note |

|--------------------------|------------------|------|------|------|------|

| Input Capacitance        | CIN              |      | 10   | pF   | 1    |

| Input/Output Capacitance | C <sub>OUT</sub> | _    | 10   | pF   | 1    |

Note:

Sampling value. Measurement conditions are  $V_{IN} = V_{OUT} = GND$ , f = 1MHz, and  $Ta = 25^{\circ}C$

#### PACKAGE DIMENSIONS

#### Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact a ROHM sales office for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

#### **Revision History**

|                |               | Pa                  | age                |                 |

|----------------|---------------|---------------------|--------------------|-----------------|

| Document No.   | Date          | Previous<br>Edition | Current<br>Edition | Description     |

| FEDR45V064B-01 | Jan. 08, 2016 | -                   | -                  | Final edition 1 |

#### Notes

- 1) The information contained herein is subject to change without notice.

- 2) Although LAPIS Semiconductor is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. LAPIS Semiconductor shall have no responsibility for any damages arising out of the use of our Products beyond the rating specified by LAPIS Semiconductor.

- 3) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 4) The technical information specified herein is intended only to show the typical functions of the Products and examples of application circuits for the Products. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Semiconductor or any third party with respect to the information contained in this document; therefore LAPIS Semiconductor shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (i.e. AV/OA devices, communication, consumer systems, gaming/entertainment sets) as well as the applications indicated in this document.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a LAPIS Semiconductor representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) LAPIS Semiconductor shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) LAPIS Semiconductor has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Semiconductor does not warrant that such information is error-free and LAPIS Semiconductor shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. LAPIS Semiconductor shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Semiconductor.

Copyright 2016 LAPIS Semiconductor Co., Ltd.

### LAPIS Semiconductor Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-semi.com/en/