#### 20V P-CHANNEL ENHANCEMENT MODE MOSFET

### **Product Summary**

| BV <sub>DSS</sub> | Rds(on) max                     | ID MAX<br>@ T <sub>A</sub> = +25°C |  |

|-------------------|---------------------------------|------------------------------------|--|

| -20V              | 495mΩ @ V <sub>GS</sub> = -4.5V | -0.77A                             |  |

|                   | 690mΩ @ V <sub>GS</sub> = -2.5V | -0.67A                             |  |

|                   | 960mΩ @ V <sub>GS</sub> = -1.8V | -0.57A                             |  |

## **Description and Applications**

This MOSFET is designed to minimize the on-state resistance (R<sub>DS(ON)</sub>), yet maintain superior switching performance, making it ideal for high efficiency power management applications.

Portable Electronics

### **Features and Benefits**

- Footprint of just 0.6mm<sup>2</sup> 13 Times Smaller than SOT23

- 0.4mm Profile Ideal for Low Profile Applications

- Low Gate Threshold Voltage

- · Fast Switching Speed

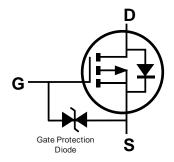

- ESD Protected Gate

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please <u>contact us</u> or your local Diodes representative. <a href="https://www.diodes.com/quality/product-definitions/">https://www.diodes.com/quality/product-definitions/</a>

#### **Mechanical Data**

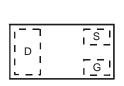

- Case: X2-DFN1006-3

- Case Material: Molded Plastic, "Green" Molding Compound.

UL Flammability Classification Rating 94V-0

- Moisture Sensitivity: Level 1 per J-STD-020

- Terminals: Finish NiPdAu over Copper Leadframe. Solderable per MIL-STD-202, Method 208

- Weight: 0.001 grams (Approximate)

**Bottom View**

Top View Internal Schematic

**Equivalent Circuit**

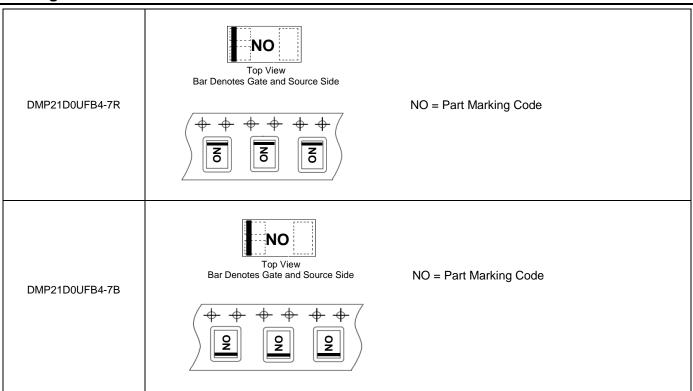

### **Ordering Information** (Note 4)

| Part Number    | Marking | Reel Size (inches) | Tape Width (mm) | Tape Pitch (mm) | Quantity per Reel |

|----------------|---------|--------------------|-----------------|-----------------|-------------------|

| DMP21D0UFB4-7R | NO      | 7                  | 8               | 4               | 3,000             |

| DMP21D0UFB4-7B | NO      | 7                  | 8               | 2               | 10,000            |

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

- 4. For packaging details, go to our website at https://www.diodes.com/design/support/packaging/diodes-packaging/.

# **Marking Information**

## Maximum Ratings (@TA = +25°C, unless otherwise specified.)

| Characteristic                |                 |                                       | Symbol | Value | Unit |

|-------------------------------|-----------------|---------------------------------------|--------|-------|------|

| Drain-Source Voltage          |                 |                                       | VDSS   | -20   | V    |

| Gate-Source Voltage           |                 | Vgss                                  | ±8     | V     |      |

| Continuous Drain Current      | 0, 1            | $T_A = +25^{\circ}C \text{ (Note 5)}$ |        | -0.77 |      |

|                               | Steady<br>State | $T_A = +85^{\circ}C \text{ (Note 5)}$ | lD     | -0.55 | Α    |

|                               | State           | T <sub>A</sub> = +25°C (Note 6)       | ]      | -1.17 |      |

| Pulsed Drain Current (Note 7) |                 | I <sub>DM</sub>                       | -5.0   | Α     |      |

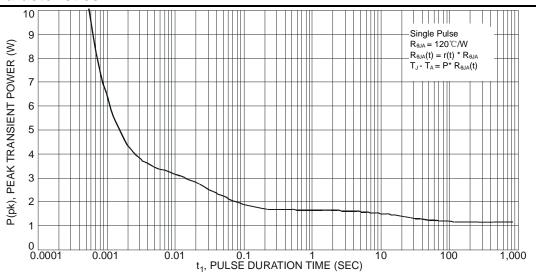

### Thermal Characteristics (@TA = +25°C, unless otherwise specified.)

| Characteristic                                   | Symbol            | Value       | Unit |

|--------------------------------------------------|-------------------|-------------|------|

| Power Dissipation (Note 5)                       | P <sub>D</sub>    | 0.43        | W    |

| Power Dissipation (Note 6)                       | P <sub>D</sub>    | 0.99        | W    |

| Thermal Resistance, Junction to Ambient (Note 5) | R <sub>θ</sub> ЈА | 293         | °C/W |

| Thermal Resistance, Junction to Ambient (Note 6) | Reja              | 126         | °C/W |

| Operating and Storage Temperature Range          | TJ, TSTG          | -55 to +150 | °C   |

Notes:

- Device mounted on FR-4 substrate PC board, 2oz copper, with minimum recommended pad layout.

Device mounted on FR-4 substrate PC board, 2oz copper, with thermal vias to bottom layer 1inch square copper plate.

- 7. Device mounted on minimum recommended pad layout test board,  $10\mu s$  pulse duty cycle = 1%.

### Thermal Characteristics

Fig. 1 Single Pulse Maximum Power Dissipation

Fig. 2 Transient Thermal Response

# Electrical Characteristics (@TA = +25°C, unless otherwise specified.)

| Characteristic                                         | Symbol              | Min  | Тур  | Max  | Unit | Test Condition                                               |  |

|--------------------------------------------------------|---------------------|------|------|------|------|--------------------------------------------------------------|--|

| OFF CHARACTERISTICS (Note 8)                           |                     |      |      |      |      |                                                              |  |

| Drain-Source Breakdown Voltage                         | BVDSS               | -20  | _    | _    | V    | $V_{GS} = 0V$ , $I_{D} = -250\mu A$                          |  |

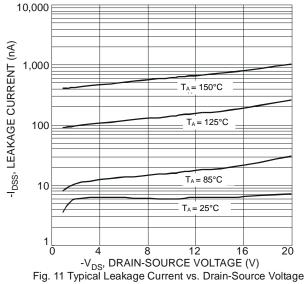

| Zero Gate Voltage Drain Current T <sub>J</sub> = +25°C | I <sub>DSS</sub>    | _    | _    | -1   | μA   | $V_{DS} = -20V, V_{GS} = 0V$                                 |  |

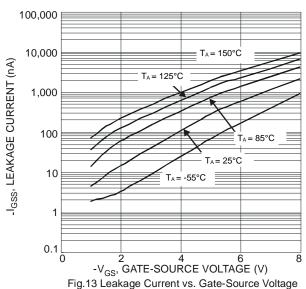

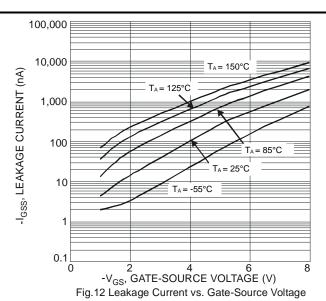

| Gate-Source Leakage                                    | Igss                | _    | _    | ±10  | μA   | $V_{GS} = \pm 8V$ , $V_{DS} = 0V$                            |  |

| ON CHARACTERISTICS (Note 8)                            |                     |      |      |      |      |                                                              |  |

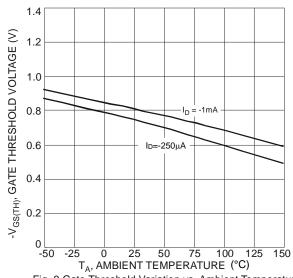

| Gate Threshold Voltage                                 | V <sub>GS(TH)</sub> | -0.5 | -0.7 | -1.0 | V    | $V_{DS} = V_{GS}, I_{D} = -250 \mu A$                        |  |

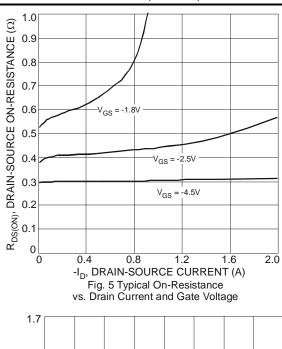

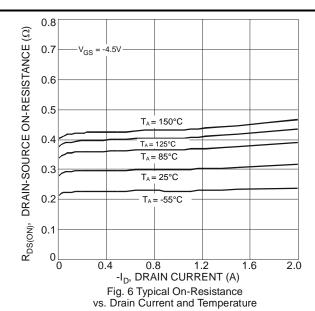

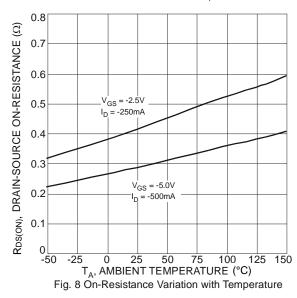

|                                                        |                     |      |      | 495  |      | $V_{GS} = -4.5V, I_{D} = -400mA$                             |  |

| Static Drain-Source On-Resistance                      | R <sub>DS(ON)</sub> | _    | _    | 690  | mΩ   | $V_{GS} = -2.5V, I_D = -300mA$                               |  |

|                                                        |                     |      |      | 960  | 1    | V <sub>G</sub> S = -1.8V, I <sub>D</sub> = -100mA            |  |

| Forward Transfer Admittance                            | Yfs                 | 50   | _    | _    | ms   | $V_{DS} = -3V, I_{D} = -300 \text{mA}$                       |  |

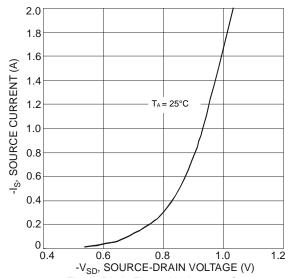

| Diode Forward Voltage                                  | VsD                 | _    | _    | -1.2 | V    | V <sub>G</sub> S = 0V, I <sub>S</sub> = -300mA               |  |

| DYNAMIC CHARACTERISTICS (Note 9)                       |                     |      |      |      |      |                                                              |  |

| Input Capacitance                                      | Ciss                | _    | 76.5 | _    | pF   | 101/11/                                                      |  |

| Output Capacitance                                     | Coss                | _    | 13.7 | _    | pF   | V <sub>DS</sub> = -10V, V <sub>GS</sub> = 0V,<br>-f = 1.0MHz |  |

| Reverse Transfer Capacitance                           | Crss                | _    | 10.7 | _    | pF   | 1 = 1.01/11/12                                               |  |

| Gate Resistance                                        | Rg                  | _    | 195  | _    | Ω    | $V_{DS} = 0V$ , $V_{GS} = 0V$ , $f = 1MHz$                   |  |

| Total Gate Charge                                      | Qg                  | _    | 1.5  | _    | nC   | VGS = -8V, VDS = -15V, ID = -1A                              |  |

| Total Gate Charge                                      | Qg                  | _    | 1.0  | _    | nC   | V 45V V 45V                                                  |  |

| Gate-Source Charge                                     | Qgs                 | _    | 0.2  | _    | nC   | V <sub>G</sub> S = -4.5V, V <sub>D</sub> S = -15V,           |  |

| Gate-Drain Charge                                      | Qgd                 | _    | 0.3  | _    | nC   | I <sub>D</sub> = -1A                                         |  |

| Turn-On Delay Time                                     | t <sub>D(ON)</sub>  | _    | 7.1  | _    | ns   |                                                              |  |

| Turn-On Rise Time                                      | t <sub>R</sub>      | _    | 8.0  | _    | ns   | V <sub>DS</sub> = -10V, -I <sub>D</sub> = 1A                 |  |

| Turn-Off Delay Time                                    | tD(OFF)             | _    | 31.7 | _    | ns   | $V_{GS} = -4.5V$ , $R_g = 6\Omega$                           |  |

| Turn-Off Fall Time                                     | tF                  |      | 18.5 | _    | ns   |                                                              |  |

Notes:

- 8. Short duration pulse test used to minimize self-heating effect. 9. Guaranteed by design. Not subject to product testing.

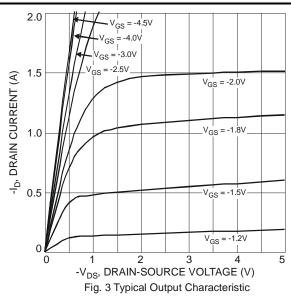

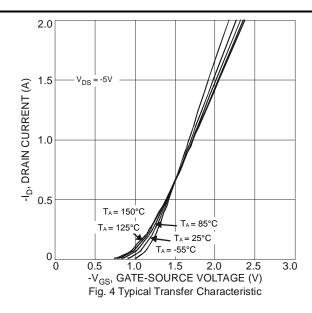

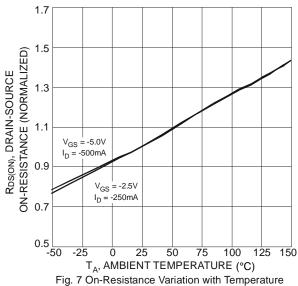

# **Typical Characteristics**

# Typical Characteristics (continued)

Fig. 9 Gate Threshold Variation vs. Ambient Temperature

## Typical Characteristics (continued)

8 -V<sub>GS</sub>, GATE-SOURCE VOLTAGE (V) V<sub>DS</sub> = -15V 2 0. 0.4 0.6 0.8 1.0 1.2 Q<sub>g</sub>, TOTAL GATE CHARGE (nC) Fig. 15 Gate-Charge Characteristics

1,000 f = 1MHz C<sub>T</sub>, JUNCTION CAPACITANCE (pF) 100 4 6 8 10 12 14 16 1 -V<sub>DS</sub>, DRAIN-SOURCE VOLTAGE (V) Fig. 14 Typical Junction Capacitance

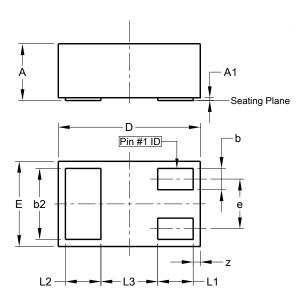

### **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

#### X2-DFN1006-3

| X2-DFN1006-3 |                      |      |      |  |  |  |

|--------------|----------------------|------|------|--|--|--|

| Dim          | Min                  | Max  | Тур  |  |  |  |

| Α            | _                    | 0.40 | _    |  |  |  |

| A1           | 0.00                 | 0.05 | 0.03 |  |  |  |

| b            | 0.10                 | 0.20 | 0.15 |  |  |  |

| b2           | 0.45                 | 0.55 | 0.50 |  |  |  |

| D            | 0.95                 | 1.05 | 1.00 |  |  |  |

| Е            | 0.55                 | 0.65 | 0.60 |  |  |  |

| е            |                      |      | 0.35 |  |  |  |

| L1           | 0.20                 | 0.30 | 0.25 |  |  |  |

| L2           | 0.20                 | 0.30 | 0.25 |  |  |  |

| L3           | _                    | _    | 0.40 |  |  |  |

| Z            | 0.02                 | 0.08 | 0.05 |  |  |  |

| All Di       | All Dimensions in mm |      |      |  |  |  |

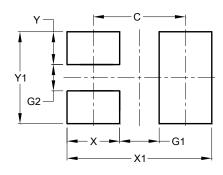

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

#### X2-DFN1006-3

| Dimensions | Value (in mm) |

|------------|---------------|

| С          | 0.70          |

| G1         | 0.30          |

| G2         | 0.20          |

| Х          | 0.40          |

| X1         | 1.10          |

| Y          | 0.25          |

| Y1         | 0.70          |

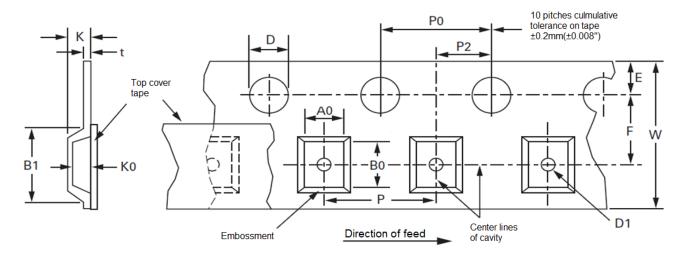

# **Embossed Carrier Tape Specifications**

Please see http://www.diodes.com/package-outlines.html for the latest version.

| Tape Width (W) | Dimension | Value (mm)                                                                                                                                                                                                                    | Dimension | Value (mm)                | Dimension | Value (mm) |

|----------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------|-----------|------------|

| 8mm            | B1        | 4.5 max.                                                                                                                                                                                                                      | F         | 3.5±0.05                  | P2        | 2.0±0.05   |

|                | D         | 1.5+0.10 -0.0                                                                                                                                                                                                                 | К         | 2.4 max.                  | t         | 0.40 max.  |

|                | D1        | 0.35 min.                                                                                                                                                                                                                     | Р         | 4.0±0.10<br>2.0±0.05(-7B) | w         | 8±0.30     |

|                | E         | 1.75±0.10                                                                                                                                                                                                                     | P0        | 4.0±0.10                  |           |            |

|                | A0 B0 K0  | Determined by component size. The clearance between the component and the cavity must complete the rotational and lateral movement requirement provided in figures in the "Maximum Componer Movement in Tape Pocket" section. |           |                           |           |            |

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2019, Diodes Incorporated

www.diodes.com