# Ultra-Low I<sub>Q</sub> Load-Switch Controller with RESET Timer

# **DESCRIPTION**

The MP6412 is a load-switch controller used to turn the main-power P-channel MOSFET on and off. The MP6412 has a 2.2V to 12V operating input voltage range. The MP6412 is a space-saving solution for smartphones, tablets, and other portable device applications.

The MP6412 is equipped with reset and power sequence functions with a factory-programmable delay timer. The reset and power sequence are controlled by the RST0/RST1 and OFF signals. The MP6412 also has a system discharge path, shipping mode and charger insert detection feature.

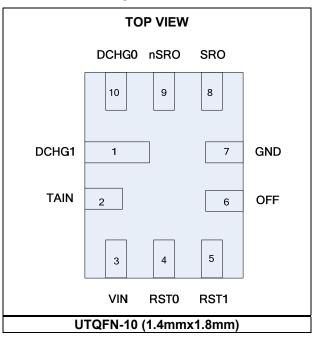

The MP6412 is available in a UTQFN-10 (1.4mmx1.8mm) package.

# **FEATURES**

- V<sub>IN</sub> Range from 2.2V to 12V

- P-MOSFET Gate Driver

- Auto 150Ω Output Discharge

- <2µA Quiescent Current</li>

- <1µA Shipping Mode Current</li>

- Factory-Fixed Reset Delay

- ESD HBM 2kV

- Available in a Space-Saving UTQFN-10 (1.4mmx1.8mm) Package

# **APPLICATIONS**

- Mobile Phones

- Portable/Handheld Devices

- Wearable Devices

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

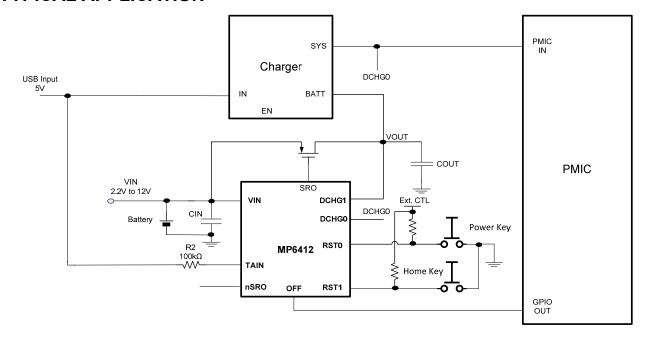

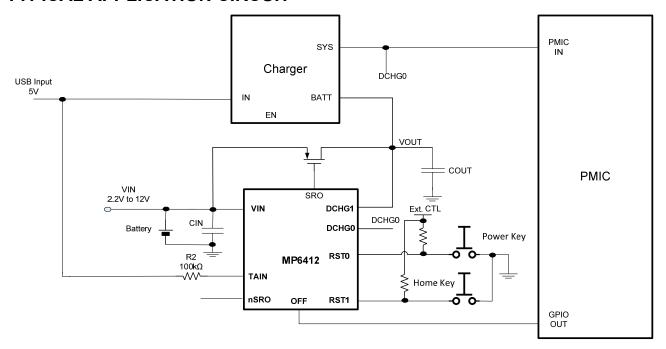

# TYPICAL APPLICATION

# ORDERING INFORMATION

| Part Number* | Package                | Top Marking |  |  |

|--------------|------------------------|-------------|--|--|

| MP6412GQGU   | UTQFN-10 (1.4mmx1.8mm) | See Below   |  |  |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP6412GQGU–Z).

# **TOP MARKING**

FV

LL

FV: Product code of MP6412GQGU

LL: Lot number

# **PACKAGE REFERENCE**

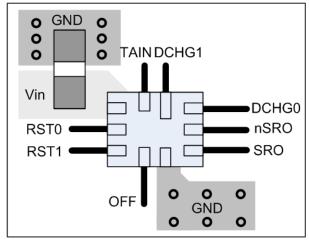

# PIN FUNCTIONS

| Pin# | Name  | Description                                                                                                                                                                                               |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | DCHG1 | Path 1 discharge pin. DCHG1 begins to discharge when the MP6412 enters RESET mode and TAIN is low.                                                                                                        |

| 2    | TAIN  | <b>Charger insert detection pin.</b> TAIN pulls down to GND internally through a resistor. When a charger is inserted, TAIN is pulled high by an external charger.                                        |

| 3    | VIN   | Input power supply.                                                                                                                                                                                       |

| 4    | RST0  | Reset input 0. RST0 is active low. Do not float RST0.                                                                                                                                                     |

| 5    | RST1  | Reset input 1. RST1 is active low. Do not float RST1.                                                                                                                                                     |

| 6    | OFF   | Function to turn off external P-FET to enter shipping mode. OFF pulls down to GND internally through a resistor.                                                                                          |

| 7    | GND   | Ground.                                                                                                                                                                                                   |

| 8    | SRO   | <b>System reset output signal.</b> SRO is the push-pull output. SRO has an external P-FET gate driver.                                                                                                    |

| 9    | nSRO  | <b>System reset output negative signal.</b> nSRO is an open-drain output. When SRO is low, the open-drain MOSFET is off. When SRO is high, the open-drain MOSFET is on. nSRO is floated in shipping mode. |

| 10   | DCHG0 | Path 0 discharge pin. DCHG0 begins to discharge when the MP6412 enters RESET mode and TAIN is low.                                                                                                        |

# ABSOLUTE MAXIMUM RATINGS (1)

| Supply voltage (V <sub>IN</sub> )                                               | 0.3V to 14V                  |

|---------------------------------------------------------------------------------|------------------------------|

| V <sub>RST0/RST1</sub>                                                          |                              |

| V <sub>OFF</sub>                                                                | 0.3V to 6V                   |

| V <sub>TAIN</sub> , V <sub>DCHG0/1</sub> , V <sub>SRO</sub> , V <sub>nSRO</sub> | 0.3V to 14V                  |

| Junction temperature                                                            |                              |

| Lead temperature                                                                | 260°C                        |

| Continuous power dissipation (T                                                 | $_{A} = +25^{\circ}C)^{(2)}$ |

|                                                                                 | 0.9W                         |

| Storage temperature                                                             |                              |

# Recommended Operating Conditions (3) Supply voltage (V<sub>IN</sub>) ...... 2.2V to 12V V<sub>RST0/RST1</sub> ..... 0V to 5.5V V<sub>OFF</sub> ...... 0V to 5.5V V<sub>TAIN</sub>, V<sub>DCHG0</sub>, V<sub>DCHG1</sub> ...... 0V to 12V Operating junction temp. (T<sub>J</sub>)....-40°C to +125°C

Thermal Resistance (4)  $\theta_{JA}$   $\theta_{JC}$ UTQFN-10 (1.4mmx1.8mm) .... 140 .. 30 ... °C/W

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{\text{JA}}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$ (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- Measured on JESD51-7, 4-layer PCB. The value of  $\theta_{JA}$  given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values are calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

$V_{\text{IN}}$  = 3.6V,  $T_{\text{J}}$  = -40°C to +125°C, typical value is tested at  $T_{\text{J}}$  = 25°C. The limit over temperature is guaranteed by characterization, unless otherwise noted.

| Parameters                                | Symbol            | Condition                                                                     | Min                  | Тур  | Max | Units |

|-------------------------------------------|-------------------|-------------------------------------------------------------------------------|----------------------|------|-----|-------|

| Input and Supply Voltage Range            | )                 |                                                                               |                      |      |     |       |

| Input voltage                             | $V_{IN}$          |                                                                               | 2.2                  |      | 12  | V     |

| Supply Current                            |                   |                                                                               |                      |      |     |       |

| Shipping mode current                     | $I_{OFF}$         | V <sub>IN</sub> = 3.6V, load switch off, shipping mode                        |                      | 0.75 | 1.5 | μA    |

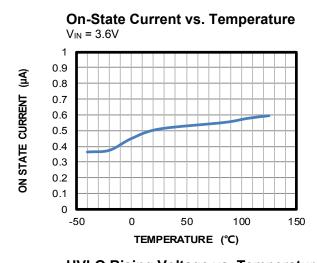

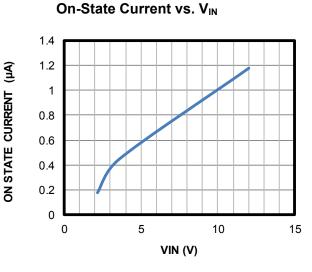

|                                           | I <sub>ON1</sub>  | V <sub>IN</sub> = 3.6V, load switch on, no load, no action assert             |                      |      | 2   | μA    |

| On state current                          | I <sub>ON2</sub>  | V <sub>IN</sub> = 3.6V, load switch on, no load, action assert to turn OSC on |                      |      | 10  | μA    |

| Gate Driver                               |                   |                                                                               |                      |      |     |       |

| SRO rising time                           | $T_{Rise}$        | V <sub>IN</sub> = 4V, Qg = 20nC                                               | 1                    | 2    | 3   | ms    |

| SRO falling time                          | T <sub>Fall</sub> | $V_{IN}$ = 4V, Qg = 20nC                                                      | 1                    | 2    | 3   | ms    |

| SRO rising delay (5)                      | $T_{SRO}$         | Between V <sub>IN</sub> good and SRO starting to fall                         | 1                    | 2    | 3   | ms    |

| SRO logic high level                      |                   |                                                                               | V <sub>IN</sub> -0.3 |      |     | V     |

| SRO logic low level                       |                   |                                                                               |                      |      | 0.3 | V     |

| V <sub>DCHG0/1</sub> discharge resistance |                   | Force 1mA current                                                             |                      | 70   | 120 | Ω     |

|                                           |                   | $V_{DCH0/1} = 4V$                                                             |                      | 150  |     | Ω     |

| Discharge delay (5)                       | $T_DD$            |                                                                               | 4                    | 5    | 6   | ms    |

| Under-Voltage Protection (UVP)            |                   | 1                                                                             | 1                    |      |     | T     |

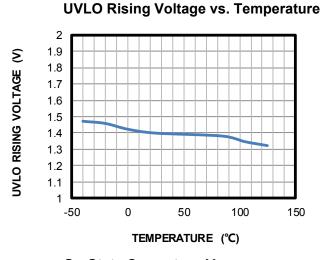

| VIN under-voltage lockout threshold       | VIN_UVLO          |                                                                               |                      | 1.43 |     | V     |

| UVLO hysteresis (6)                       | Vuvlohys          |                                                                               |                      | 500  |     | mV    |

| RST0/RST1/OFF Logic (Input)               |                   |                                                                               |                      |      |     |       |

| RST0/1 high level                         | $V_{H}$           |                                                                               | 1                    |      |     | V     |

| RST0/1 low level                          | VL                |                                                                               |                      |      | 0.4 | V     |

| OFF high level                            | V <sub>HOFF</sub> |                                                                               | 1                    |      |     | V     |

| OFF low level                             | $V_{LOFF}$        |                                                                               |                      |      | 0.4 | V     |

| OFF pull-down resistor                    |                   |                                                                               |                      | 1    |     | ΜΩ    |

| RST0/RST1 leakage current                 |                   | $V_{IN} = V_{RST0} = V_{RST1} = 3.6V$                                         |                      |      | 150 | nA    |

| D. L. (5)                                 | T <sub>DG1</sub>  | RST0, RST1, TAIN                                                              |                      | 10   |     | ms    |

| Debounce time (5)                         | $T_{DG2}$         | OFF                                                                           |                      | 250  |     | μs    |

| nSRO Logic (Open-Drain Output             |                   | 1                                                                             |                      |      |     |       |

| High level                                | ,                 | $V_{IN}$ = 3.3V, pull up $V_{IN}$ through external 100kΩ                      | V <sub>IN</sub> *0.8 | Vin  |     | V     |

| Low level                                 |                   | Sink 1mA                                                                      |                      |      | 0.4 | V     |

| nSRO leakage current/logic high           |                   | $V_{IN}$ = 3.3V, pull up $V_{IN}$<br>through external 100kΩ                   |                      | 50   |     | nA    |

| TAIN Logic (Input)                        |                   |                                                                               | 1                    |      |     | I.    |

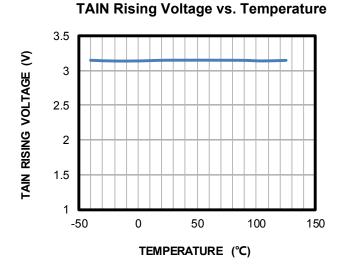

| TAIN rising                               |                   |                                                                               | 2.8                  | 3.15 | 3.5 | V     |

| TAIN hysteresis                           |                   |                                                                               | 1.0                  | 100  |     | mV    |

| TAIN confirm delay (5)                    | T <sub>7</sub>    |                                                                               | 40                   | 50   | 60  | ms    |

| TAIN internal pull-down resistor          | - 1               |                                                                               |                      | 2    |     | MΩ    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{\text{IN}}$  = 3.6V,  $T_{\text{J}}$  = -40°C to +125°C, typical value is tested at  $T_{\text{J}}$  = 25°C. The limit over temperature is guaranteed by characterization, unless otherwise noted.

| Parameters                 | Symbol         | Condition            | Min  | Тур | Max  | Units |

|----------------------------|----------------|----------------------|------|-----|------|-------|

| RESET Time (5)             |                |                      |      |     |      |       |

| Power RESET entry time (5) | T <sub>1</sub> |                      | 8    | 10  | 12   | S     |

| Power RESET off time (5)   | T <sub>2</sub> |                      | 0.32 | 0.4 | 0.48 | S     |

| Turn-off response time (5) | T <sub>3</sub> |                      | 1    | 1.5 | 2    | ms    |

| Turn-off confirm cycle (6) |                |                      |      | 5   |      |       |

| Turn-off confirm time (5)  | T <sub>4</sub> |                      | 80   | 100 | 120  | ms    |

| Turn-off delay time (5)    | T <sub>5</sub> |                      | 12   | 15  | 18   | S     |

| Turn-on response time (5)  | T <sub>6</sub> |                      | 1.6  | 2   | 2.4  | S     |

| SRO pull-up current        |                | V <sub>IN</sub> = 4V |      | 1.3 |      | μA    |

#### NOTES:

- 5) Guaranteed by correlation.

- 6) Guaranteed by engineering sample test, not tested in production.

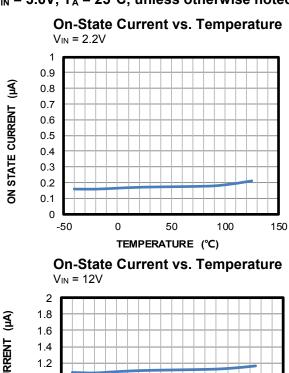

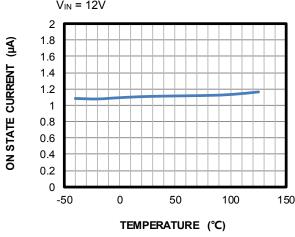

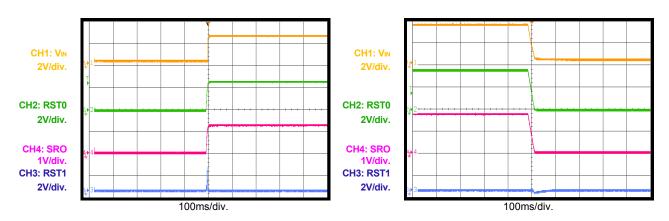

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  = 3.6V,  $T_A$  = 25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 3.6V,  $T_A$  = 25°C, unless otherwise noted.

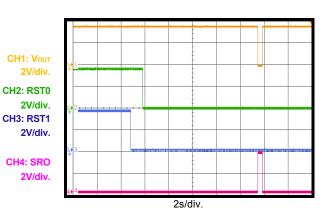

# **Reset Function**

# CH1: Vour 2V/div. CH2: RST0 2V/div. CH3: RST1 2V/div. CH4: SRO 2V/div. Zs/div.

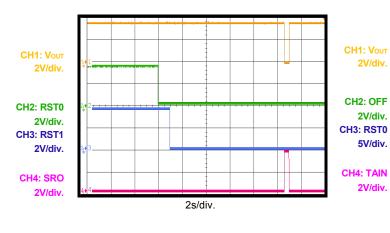

# **Reset Function (RST1 First)**

# **Reset Function (RST0 First)**

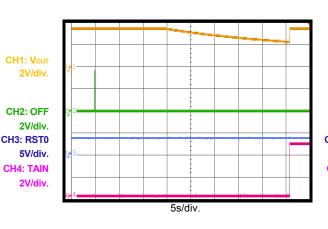

# **Shipping Mode Enter**

# **Shipping Mode Exit with TAIN**

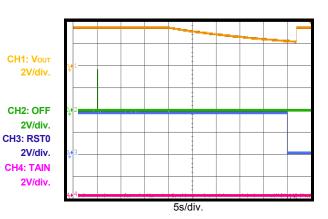

# **Shipping Mode Exit with RST0**

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}$  = 3.6V,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

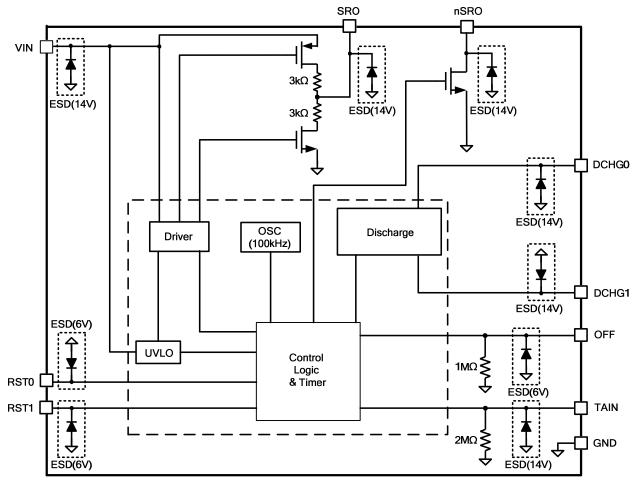

# **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

### **OPERATION**

The MP6412 is a load-switch controller to turn the main power P-channel MOSFET on and off. The MP6412 has a 2.2V to 12V operating input voltage range. The MP6412 provides a space-saving solution for smartphones, tablets, and other portable device applications.

The MP6412 is equipped with reset and power sequence functions with a factory-programmable delay timer. The reset and power sequence are controlled by the RST0/RST1 and OFF signals. For mobile applications, the MP6412 has two discharge paths and a charger insert detection feature.

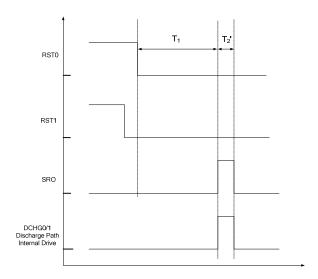

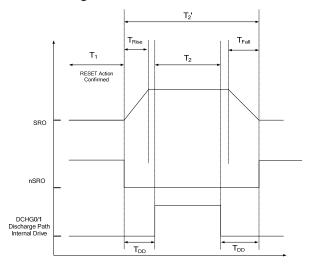

# **Reset Function (RESET)**

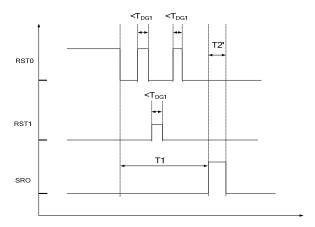

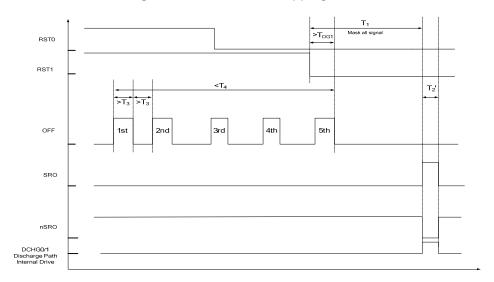

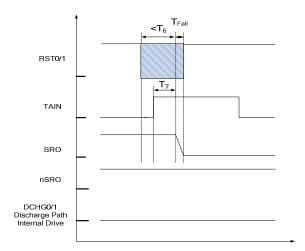

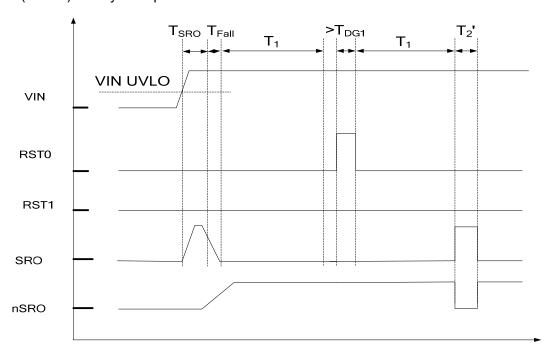

The MP6412 can reset the system by turning off the external power MOSFET (load switch) if needed. This action clears the current status and restarts to the initial status by cutting off the power supply of the down-stream system. Enter the RESET function by pulling both RST0 and RST1 down to logic low for 10s (Note that  $T_2$ ' =  $T_2 + T_{DD} \times 2$ ).

Figure 2 and Figure 3 show the waveforms during a  $T_2$ ' RESET action.

To avoid an erroneous RST0/1 trigger, a debounce time (TDG1) can be implemented. If the logic glitch duration is less than TDG1, the logic glitch is ignored (see Figure 4).

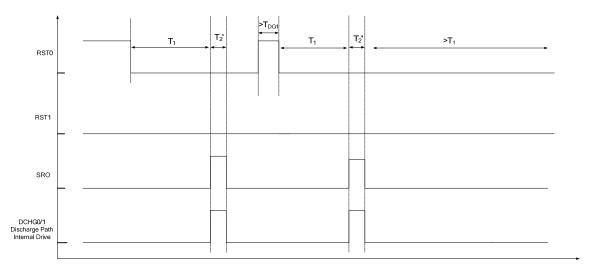

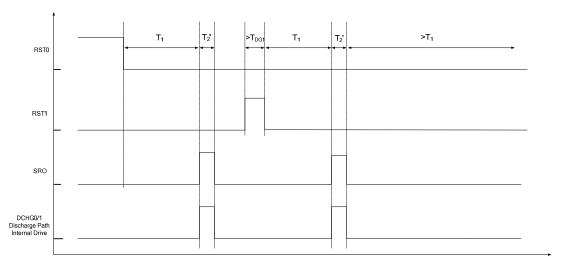

In normal operation, if the MP6412 detects that both RST0 and RST1 are low for 10s, the MP6412 turns off the load switch for  $T_2$ ' (400 + 10ms) and restarts it. During the 400ms off time, DCHG0 and DCHG1 turn on their respective discharge path to pull down the  $V_{\text{OUT}}$  and system voltage to clear out the current status. The RESET function can be activated once RST0 and RST1 are both active. The next RESET function is active after the RST0 or RST1 logic changes again (See Figure 5 and Figure 6).

Figure 2: RESET Procedure

Figure 3: SRO and Discharge Procedure

**Figure 4: Debounce Procedure**

Figure 5: Multiple RST0 Reset

Figure 6: Multiple RST1 Reset

During  $T_1$  (after RST0/1 both drop low) and  $T_2$ ' (if a RESET action occurs), the RESET action has the highest priority. This action masks the high TAIN logic or shipping mode trigger signal. During  $T_1$  and its follow RESET period, all signals are ignored. Refer to the Enter/Exit Shipping Mode sections on page 11 and page 13.

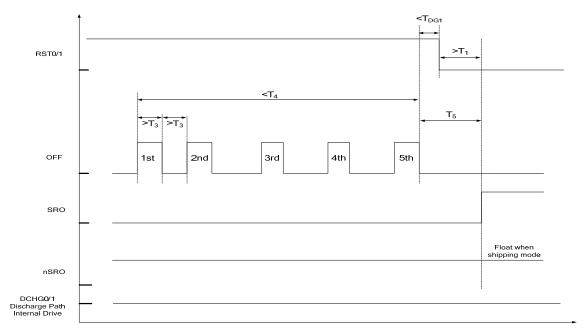

### **Enter Shipping Mode**

The MP6412 can fully turn off the load switch to achieve a very small shutdown current. In this mode, the MP6412 cuts off the battery from the system. Therefore, the battery energy can be stored for a long time due to the low consumption current of the MP6412 in shipping mode.

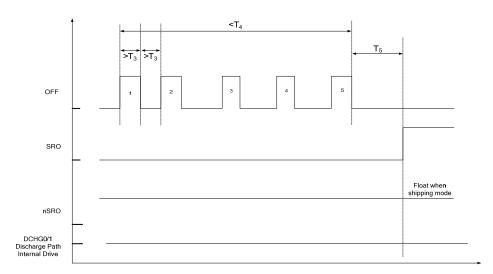

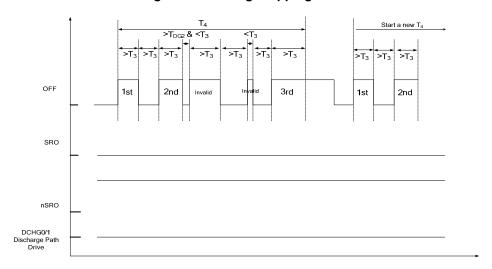

In normal status, a specific OFF pin signal (on time more than  $T_3$ , off time more than  $T_3$ , repeat five cycles in 100ms) makes the MP6412 turn off the load switch and enter shipping mode. Afterward, nSRO is floated (see Figure 7). The discharge function is not active in this mode.

If the enter shipping mode signal is confirmed, all signals are ignored during  $T_5$ .

To avoid an erroneous OFF trigger, a debounce time (TDG2) can be implemented. If the logic glitch duration is less than TDG2, the logic glitch will be ignored (see Figure 8).

The OFF signal has lower priority than RST0/1 signal. OFF is terminated if RST0/1 low occurs (see Figure 9).

Figure 7: Entering Shipping Mode

Figure 8: Cannot Enter Shipping Mode

Figure 9: OFF Priority Procedure

The OFF signal has higher priority than the TAIN signal. After the OFF signal is confirmed, the high TAIN signal can exit the MP6412 from shipping mode (see Figure 10).

Figure 10: OFF Priority Procedure

# **Exiting Shipping Mode**

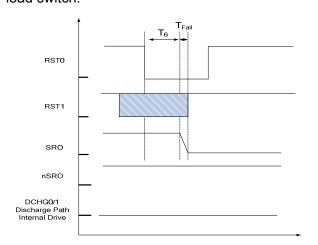

The MP6412 turns on the load switch when exiting shipping mode.

In shipping mode, when the RST0 signal is pulled down for 2s and  $V_{\text{IN}}$  is higher than its under-voltage lockout (UVLO) threshold, the MP6412 exits shipping mode and turns on the load switch.

Figure 11: Shipping Mode Exit Procedure

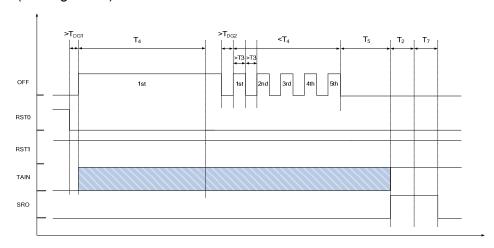

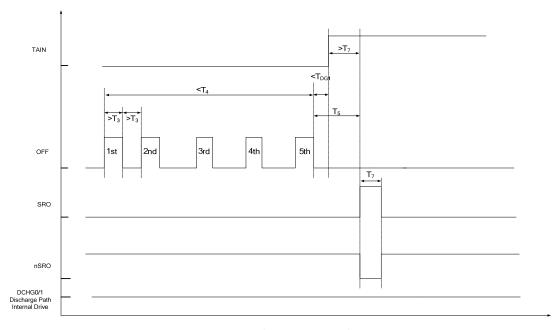

In addition to RST0, a high TAIN signal can also make the MP6412 exit shipping mode. TAIN is connected to the power jack through a  $100k\Omega$  resistor, typically. When a charger is inserted, TAIN monitors a high logic, which can also make the MP6412 exit shipping mode. Figure 12 shows the MP6412 in shipping mode initially. TAIN and RST0 can both be used to

make the MP6412 exit shipping mode, but the MP6412 must confirm the action of TAIN first.

Figure 12: TAIN Procedure

When the MP6412 is in shipping mode, a RST0 or TAIN input is required to exit shipping mode. The RST0 input requires a logic change to enable the confirmation sequence. If RST0 is dead low when the OFF confirm time is triggered, the MP6412 does not exit shipping mode (see Figure 13). If TAIN is dead high when the OFF confirm time is triggered, the shipping mode logic cannot be masked (see Figure 14).

Figure 13: RST0/1 Not Exiting Shipping

Figure 14: TAIN Cycle Exiting Shipping

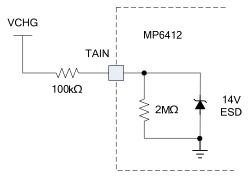

# **TAIN Feature**

TAIN is connected to an external charger through a  $100k\Omega$  resistor. TAIN has an internal  $2M\Omega$  pull-down resistor to ground. The external and internal resistors form a resistor-divider circuit. The TAIN voltage can be calculated with Equation (1):

$$V(TAIN) = \frac{R_{Int}}{R_{Int} + R_{Ext}} \times V(Charger)$$

(1)

Where V(TAIN) is the TAIN voltage, V(Charger) is the external charger voltage,  $R_{\text{Ext}}$  is the external resistor, and  $R_{\text{Int}}$  is the internal  $2M\Omega$  resistor.

When the TAIN voltage is higher than 3.3V, it is treated as an active high logic. If the MP6412 is in shipping mode, this high logic makes the MP6412 exit it.

Figure 15 shows the TAIN internal ESD structure, which is equal to a Zener diode. When VCHG is high (maximum 30V), the ESD breaks down and clamps the TAIN voltage to 14V. The internal ESD safe current is 1mA to prevent damage to the ESD Zener diode. For example, when VCHG is 30V, there is a 16V voltage between VCHG and TAIN pin, and the current through the resistor and ESD diode is  $160\mu A$ .

Figure 15: TAIN ESD Structure

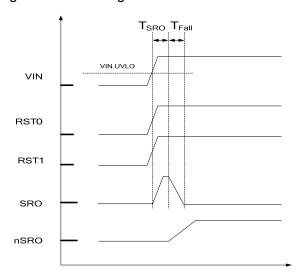

#### Power-On

When VIN rises from a very low value to the MP6412 UVLO, a power-on procedure begins. The MP6412 turns on the external P-channel MOSFET (P-FET) softly to prevent inrush

current. The power-on procedure is shown in Figure 16.

The power-on procedure is a RESET procedure and ignores the RST0 and RST1 RESET signals. To enable a RESET function, the RST0 logic must be changed.

Figure 16: Power-On Priority

Figure 17: RESET after Power-On

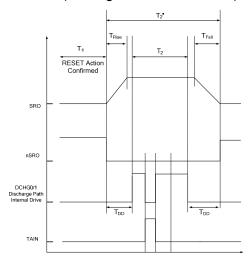

## **Discharge**

The MP6412 has two discharge paths (DCHG0/1) to release system energy during a RESET action. The DCHG0/1 path is enabled during T<sub>2</sub>. These discharge paths are through a passive resistor. If an external charger is plugged in, the passive resistor is too large to pull DCH0/1 low, and the discharge current generates a high temperature on the IC. A TAIN high logic disables DCH0/1 immediately under this situation (see Figure 18 and Table 2).

Figure 18: TAIN Disable Discharge

# **Conflicts Strategy**

The MP6412 has different response actions when RST0/RST1/OFF/TAIN has input voltage. To prevent input conflicts, refer to Table 1.

**Table 1: Signal Priority**

| Priority | Action |

|----------|--------|

| 1        | RESET  |

| 2        | OFF    |

| 3        | TAIN   |

RESET has the highest priority. The MP6412 only answers the highest priority requirement if several actions occur at the same time.

If some actions are active at the same time and one of these actions is confirmed first, the other actions will be ignored. For example, if the OFF action is confirmed first, the MP6412 enters shipping mode after 15s. In this period, RST0/RST1/TAIN cannot terminate it.

#### nSRO Function

The nSRO output is an open-drain output. Its output indicates the main power MOSFET status. When the main power MOSFET is on, it output a high logic. Otherwise, it outputs a low logic. nSRO does not have a soft on/off effect like SRO. The nSRO signal floats if the MP6412 enters shipping mode.

**Table 2: State Change Table**

|                | Event 0 |      |      |      |             | STATE0 |      |       | Event0           | STATE1 |      |       | Duration between  | STATE2 |      |       |

|----------------|---------|------|------|------|-------------|--------|------|-------|------------------|--------|------|-------|-------------------|--------|------|-------|

|                | VIN     | RST0 | RST1 | TAIN | OFF         | SRO    | nSRO | DCHGx | For (in seconds) | SRO    | nSRO | DCHGx | state1<br>and 2   | SRO    | nSRO | DCHGx |

| POR            | Ť       | х    | х    | x    | x           | 0      | Open | Open  | T <sub>SRO</sub> | Н      | х    | x     | T <sub>Fall</sub> | L      | Open | Open  |

|                | VIN     | L    | н    | x    | x           | L      | Open | Open  |                  | L      | Open | Open  |                   | L      | Open | Open  |

| RESET          | VIN     | L    | L    | н    | x           | L      | Open | Open  | T1               | t      | ı,   | Open  | T2'               | ı      | 1    | Open  |

| KESEI          | VIN     | L    | L    | L    | x           | L      | Open | Open  | T1               | t      | 1    | 1     | T2'               | 1      | 1    | 1     |

|                | VIN     | н    | L    | x    | x           | L      | Open | Open  |                  | L      | Open | Open  |                   | L      | Open | Open  |

|                | VIN     | н    | x    | x    | 5<br>pulse  | L      | Open | Open  | Т5               | 1      | Open | Open  | 0                 | н      | Open | Open  |

|                | VIN     | x    | н    | x    | 5<br>pulse  | L      | Open | Open  | Т5               | 1      | Open | Open  | 0                 | Н      | Open | Open  |

| Enter<br>Sleep | VIN     | х    | х    | x    | н           | L      | Open | Open  |                  | L      | Open | Open  |                   | L      | Open | Open  |

|                | VIN     | х    | х    | х    | L           | L      | Open | Open  |                  | L      | Open | Open  |                   | L      | Open | Open  |

|                | VIN     | x    | x    | x    | <5<br>pulse | L      | Open | Open  |                  | L      | Open | Open  |                   | L      | Open | Open  |

| Exit<br>Sleep  | VIN     | н    | х    | L    | х           | Н      | Open | Open  |                  | н      | Open | Open  |                   | н      | Open | Open  |

|                | VIN     | х    | х    | н    | х           | н      | Open | Open  | T7=50m           | н      | Open | Open  | T <sub>FALL</sub> | L      | Open | Open  |

|                | VIN     | L    | x    | х    | x           | н      | Open | Open  | T6=2             | н      | Open | Open  |                   | L      | Open | Open  |

# APPLICATION INFORMATION

# **Selecting the Input Capacitor**

Input capacitors are important for protecting the MP6412 from input voltage spikes when a  $V_{\text{IN}}$  hot-plug occurs. 0603 ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. For most applications, a 1µF 0603 input capacitor is sufficient.

# **PCB Layout Guidelines**

Efficient PCB layout is critical for stable operation. For the best results, refer to Figure 19.

Top Layer

Bottom Layer Figure 19: Recommended Layout

# TYPICAL APPLICATION CIRCUIT

**Figure 20: Typical Application Circuit**

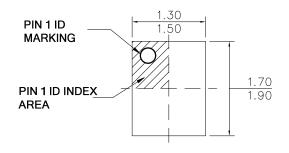

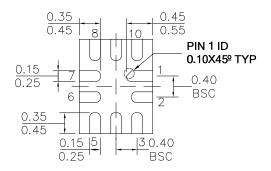

# PACKAGE INFORMATION

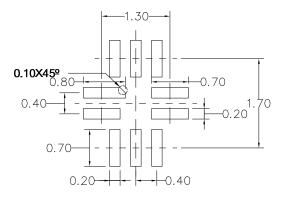

# **UTQFN-10 (1.4mmx1.8mm)**

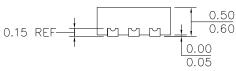

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

RECOMMENDED LAND PATTERN

# NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

- 3) JEDEC REFERENCE IS MO-220.

- 4) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.