# **Bluetooth**<sup>®</sup> Low Energy SoC

#### **Features**

- Bluetooth smart 5.0 Bluetooth Low Energy compliant

- · 256 Kbytes embedded Flash memory

- UART/SPI/I<sup>2</sup>C interface supported

- Integrated crystal oscillator operates with 32 MHz external crystal

- · Temperature sensor supported

- 31 general purpose I/O (GPIO) pins for IS1870 SoC and 15 GPIO pins for IS1871 SoC

- Supports 4-channel pulse-width modulation (PWM) for IS1870 SoC and 1-channel PWM for IS1871 SoC

- Supports 12-bit ADC (ENOB=10 or 8 bits) for battery and voltage detection

- 16-channel ADC for IS1870 SoC and 6-channel ADC for IS1871 SoC are provided

- · AES-CMAC hardware engine

- · Beacon support

- Low power consumption

- · Compact size:

- IS1871: 4 mm x 4 mm 32QFN package

- IS1870: 6 mm x 6 mm 48QFN package

## Radio Frequency (RF)/Analog Features

- · ISM band: 2.402 GHz to 2.480 GHz operation

- · Channels: 0 to 39

- Rx sensitivity: -90 dBm in Bluetooth Low Energy mode

- Tx power: 0 dBm (typical)

- Received Signal Strength Indicator (RSSI) monitor

### **Operating Conditions**

- · Operating voltage: 1.9V to 3.6V

- Operating temperature: -40°C to +85°C

## **Applications**

- Internet of Things (IoT)

- · Wearable, fitness or healthcare

- · Weighing scale

- · Proximity/Find Me services

- · Secure payment

- · Digital beacons

- · Consumer appliances or home automation

- Industrial

## **Packages**

| Туре               | IS1870  | IS1871  |

|--------------------|---------|---------|

| Pin count          | 48      | 32      |

| I/O pins (up to)   | 31      | 15      |

| Contact/lead pitch | 0.4     | 0.4     |

| Dimensions         | 6x6x0.9 | 4x4x0.9 |

| Package            | QFN48   | QFN32   |

Note: All dimensions are in millimeters (mm) unless specified.

NOTES:

#### **Table of Contents**

| 1.0 Device Overview                      | 5  |

|------------------------------------------|----|

| 2.0 System Block Details                 | 13 |

| 3.0 Electrical Characteristics           |    |

| 4.0 Package Information                  |    |

| 5.0 Reflow Profile and Storage Condition | 27 |

| 6.0 Ordering Guide                       | 31 |

| Appendix A. Reference Circuit            | 33 |

| Appendix B: Layout Guidelines            | 37 |

| Annendix C: Revision History             | 39 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

#### 1.0 DEVICE OVERVIEW

The IS1870/71 SoC contains a 2.4 GHz transceiver, a Power Management Unit (PMU), Microchip's Bluetooth Low Energy software stack and an RF power amplifier.

The default factory configuration is designed to work with a host MCU to provide the user with an embedded Bluetooth Low Energy design setup for the IoT application domain.

Note:

Flexibility of the IS1870/71 SoC enables the user to work in a host-less implementation. In this configuration, the user can embed a full application into the IS1870/71 SoC. Contact your local Microchip representative for further guidance on obtaining this setup.

The IS1870/71 SoC provides:

- · Simple integration and programming

- · Reduced development time

- Superior Bluetooth Low Energy solution with low-cost system

- Interoperability with Apple<sup>®</sup> iOS and Android™ OS

- · Wide range of application support

With the default factory configuration, the IS1870/71 SoC supports Beacon technology, where the automation of Bluetooth Low Energy connection/control and cloud connectivity are common.

The IS1870/71 SoC is optimized to maintain a low power wireless connection. The low power consumption and flexible power management maximize the IS1870/71 SoC lifetime in battery operated devices. A wide operating temperature range enables its applications in indoor and outdoor environments (industrial temperature range is -40°C to +85°C).

The small form factor package size of the IS1870/71 SoC is designed for wearable applications. The solution providers can minimize the module size to meet the market requirements, which is commonly seen in the IoT application domain.

To operate in the 2.4 GHz ISM band radio, the IS1870/71 SoC is certified for the Bluetooth v5.0 core specification, including support for the enhanced throughput and the Federal Information Processing Standard (FIPS) compliant encryption support for secure data connections.

The IS1870/71 SoC integrates transceiver and baseband functions to decrease external components. Microchip provides free Bluetooth stack firmware to build an embedded Bluetooth Low Energy solution, using the IS1870/71 SoC.

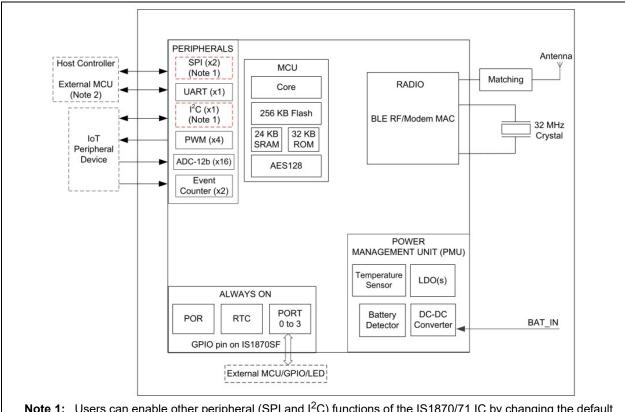

Figure 1-1 illustrates a typical block diagram of the IS1870 SoC.

#### FIGURE 1-1: BLOCK DIAGRAM OF THE IS1870 SOC

- **Note 1:** Users can enable other peripheral (SPI and I<sup>2</sup>C) functions of the IS1870/71 IC by changing the default factory firmware. For more details, contact local Microchip representatives.

- 2: An external host MCU is required when using the default factory firmware.

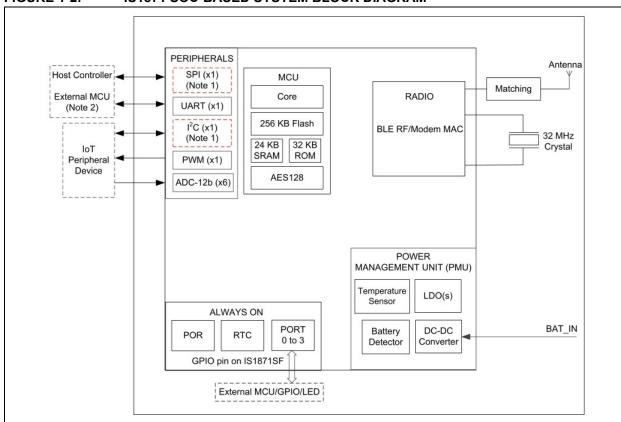

Figure 1-2 illustrates a typical block diagram of the IS1871 SoC-based system.

FIGURE 1-2: IS1871 SOC-BASED SYSTEM BLOCK DIAGRAM

- **Note 1:** Users can enable other peripheral (SPI and I<sup>2</sup>C) functions of the IS1870/71 IC by changing the default factory firmware. For more details, contact your local Microchip representatives.

- 2: An external host MCU is required when using the default factory firmware.

Table 1-1 provides the key features of the IS1870/71 SoC.

TABLE 1-1: KEY FEATURES

| Features                              | IS1870     | IS1871     |

|---------------------------------------|------------|------------|

| UART                                  | 1          | 1          |

| GPIO                                  | 31         | 15         |

| 12-bit ADC channels                   | 16         | 6          |

| PWM                                   | 4          | 1          |

| SPI (see Note 1)                      | 2          | 1          |

| I <sup>2</sup> C (see <b>Note 1</b> ) | 1          | 1          |

| Pins                                  | 48         | 32         |

| Size                                  | 6x6x0.9 mm | 4x4x0.9 mm |

| Event counter                         | 2          | 0          |

| AES-CMAC H/W engine                   | Yes        | Yes        |

**Note 1:** To make these peripherals available to a designer, contact your local Microchip representative.

## **Pin Description**

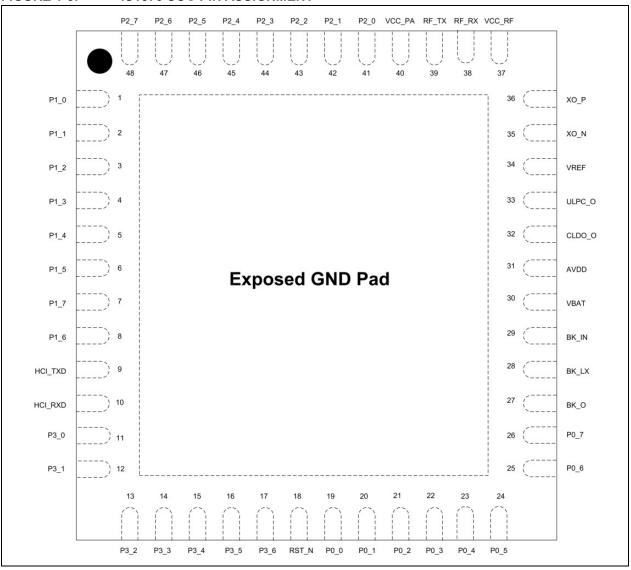

Figure 1-3 and Figure 1-4 illustrate the IS1870 and IS1871 pin assignment details.

FIGURE 1-3: IS1870 SOC PIN ASSIGNMENT

FIGURE 1-4: **IS1871 SOC PIN ASSIGNMENT** VCC\_PA P1\_0 P2\_0 P2\_7 P2\_4 30 29 28 XO\_P P1\_2 XO\_N P1\_3 VREF P1\_7 ULPC\_O P1\_6 **Exposed GND Pad** CLDO\_O HCI\_TXD AVDD HCI\_RXD VBAT P3\_1 BK\_IN P3\_2 10 12 13 14 15 16 P3\_6 P3\_4 P0\_0 P0\_2 BK\_LX

Table 1-2 provides the functions of the various pins in the IS1870/71 SoC.

TABLE 1-2: IS1870/71 SOC PIN DESCRIPTION

|                   |                   |          | DEGGIN           | 1                                                                       |

|-------------------|-------------------|----------|------------------|-------------------------------------------------------------------------|

| IS1870<br>Pin No. | IS1871<br>Pin No. | Pin Name | Туре             | Description                                                             |

| 1                 | 32                | P1_0     | DIO<br>Al        | GPIO: P1_0 ADC input: AD8 TX_CLS1: Class 1 RF Tx Control                |

| 2                 | _                 | P1_1     | DIO<br>AI<br>DI  | GPIO: P1_1 ADC input: AD9 SPI bus: MISO2: Second SPI bus (Central mode) |

| 3                 | 1                 | P1_2     | DIO<br>AI<br>I/O | GPIO: P1_2<br>ADC input: AD10<br>I <sup>2</sup> C SCL                   |

| 4                 | 2                 | P1_3     | DIO<br>AI<br>DIO | GPIO: P1_3<br>ADC input: AD11<br>I <sup>2</sup> C SDA                   |

| 5                 | _                 | P1_4     | DIO<br>AI<br>DI  | GPIO: P1_4 ADC input: AD12 Event Counter                                |

| 6                 |                   | P1_5     | DIO<br>AI<br>DI  | GPIO: P1_5 ADC input: AD13 Event Counter                                |

| 7                 | 3                 | P1_7     | DIO<br>AO        | GPIO: P1_7<br>External 32.768 kHz Crystal Output: XO32K                 |

| 8                 | 4                 | P1_6     | DIO<br>Al        | GPIO: P1_6 External 32.768 kHz Crystal Input: XI32K                     |

| 9                 | 5                 | HCI_TXD  | DO               | HCI UART TXD                                                            |

| 10                | 6                 | HCI_RXD  | DI               | HCI UART RXD                                                            |

| 11                | _                 | P3_0     | DIO              | GPIO: P3_0                                                              |

| 12                | 7                 | P3_1     | DIO<br>DO        | GPIO: P3_1<br>SPI bus: NCS, SPI Flash: CSN                              |

| 13                | 8                 | P3_2     | DIO<br>DI        | GPIO: P3_2<br>SPI bus: MISO, SPI Flash: SDO                             |

| 14                | 9                 | P3_3     | DIO<br>DO        | GPIO: P3_3<br>SPI bus: MOSI, SPI Flash: SDI                             |

| 15                | 10                | P3_4     | DIO<br>DO        | GPIO: P3_4<br>SPI bus: SCLK, SPI Flash: SCK                             |

| 16                | _                 | P3_5     | DIO<br>Al        | GPIO: P3_5<br>LED1                                                      |

| 17                | 11                | P3_6     | DIO<br>DO<br>DO  | GPIO: P3_6 UART flow-control RTS PWM0                                   |

| 18                | 12                | RST_N    | DI               | External Reset                                                          |

| 19                | 13                | P0_0     | DIO<br>AI<br>DI  | GPIO: P0_0<br>ADC input: AD0<br>UART flow-control CTS                   |

| 20                | _                 | P0_1     | DIO<br>AI        | GPIO: P0_1<br>ADC input: AD1                                            |

Legend: A = Analog D = Digital I = Input O = Output P = Power

TABLE 1-2: IS1870/71 SOC PIN DESCRIPTION (CONTINUED)

| IS1870<br>Pin No. | IS1871<br>Pin No. | Pin Name | Туре            | Description                                                                                                                                 |

|-------------------|-------------------|----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 21                | 14                | P0_2     | DIO<br>AI<br>AI | GPIO: P0_2<br>ADC input: AD2<br>LED0                                                                                                        |

| 22                | _                 | P0_3     | DIO<br>Al       | GPIO:P0_3<br>ADC input: AD3                                                                                                                 |

| 23                | _                 | P0_4     | DIO<br>Al       | GPIO:P0_4<br>ADC input: AD4                                                                                                                 |

| 24                | _                 | P0_5     | DIO<br>Al       | GPIO:P0_5 ADC input: AD5                                                                                                                    |

| 25                | _                 | P0_6     | DIO<br>Al       | GPIO:P0_6 ADC input: AD6                                                                                                                    |

| 26                | _                 | P0_7     | DIO<br>Al       | GPIO:P0_7 ADC input: AD7                                                                                                                    |

| 27                | 15                | BK_O     | Р               | 1.55V buck regulator output. For internal use, do not connect to external devices)                                                          |

| 28                | 16                | BK_LX    | Р               | 1.55V buck regulator output. For internal use, do not connect to external devices                                                           |

| 29                | 17                | BK_IN    | Р               | Buck input. Voltage Range: 1.9V to 3.6V                                                                                                     |

| 30                | 18                | VBAT     | Р               | Battery input. Voltage Range: 1.9V to 3.6V. Connect to BK_IN and a 10 μF decoupling capacitor, as illustrated in Figure A-1 and Figure A-3. |

| 31                | 19                | AVDD     | Р               | Input of LDOs: CLDO, PALDO and RFLDO                                                                                                        |

| 32                | 20                | CLDO_O   | Р               | 1.2V CLDO Output: Core-logic and memories supply, connect to 1 $\mu F$ (X5R/X7R) capacitor                                                  |

| 33                | 21                | ULPC_O   | Р               | 1.2V Programmable ULPC Output: Always On logic and retention memory supply (for internal use, do not connect to external devices)           |

| 34                | 22                | VREF     | Р               | PMU band-gap reference voltage output for LDOs and buck (for internal use, do not connect to external devices)                              |

| 35                | 23                | XO_N     | Α               | 32 MHz crystal input negative                                                                                                               |

| 36                | 24                | XO_P     | Α               | 32 MHz crystal input positive                                                                                                               |

| 37                | 25                | VCC_RF   | Р               | Power input for VCO and RF (1.28V). Connect to 1 $\mu$ F (X5R/X7R) capacitor                                                                |

| 38                | 26                | Rx       | Al              | RF receive path                                                                                                                             |

| 39                | 27                | Tx       | AO              | RF transmit path                                                                                                                            |

| 40                | 28                | VCC_PA   | Р               | Power supply for power amplifier (1.55V). Connect to 0.22 $\mu$ F X5R/X7R                                                                   |

| 41                | 29                | P2_0     | DIO             | Mode Configuration H: Application mode L: Test mode                                                                                         |

| 42                | _                 | P2_1     | DIO<br>DO       | GPIO: P2_1<br>PWM0                                                                                                                          |

| 43                | _                 | P2_2     | DIO<br>DO       | GPIO: P2_2<br>PWM1                                                                                                                          |

| 44                | _                 | P2_3     | DIO<br>DO       | GPIO: P2_3<br>PWM2                                                                                                                          |

**Legend:** A = Analog

D = Digital

I = Input

O = Output

P = Power

TABLE 1-2: IS1870/71 SOC PIN DESCRIPTION (CONTINUED)

| IS1870<br>Pin No. | IS1871<br>Pin No. | Pin Name | Туре            | Description                                                            |

|-------------------|-------------------|----------|-----------------|------------------------------------------------------------------------|

| 45                | 30                | P2_4     | DIO             | GPIO: P2_4<br>TX_CLS1: Class 1 RF RX Control                           |

| 46                | _                 | P2_5     | DIO<br>AI<br>DO | GPIO: P2_5<br>ADC input: AD15<br>PWM3                                  |

| 47                | _                 | P2_6     | DIO             | P26                                                                    |

| 48                | 31                | P2_7     | DIO<br>AI<br>DO | GPIO: P27 ADC input: AD14 SPI bus: NCS2, second SPI bus (Central mode) |

**Legend:** A = Analog D = Digital I = Input O = Output P = Power

### 2.0 SYSTEM BLOCK DETAILS

#### 2.1 System Block Descriptions

This section provides a description of the blocks used in the IS1870/71 SoC.

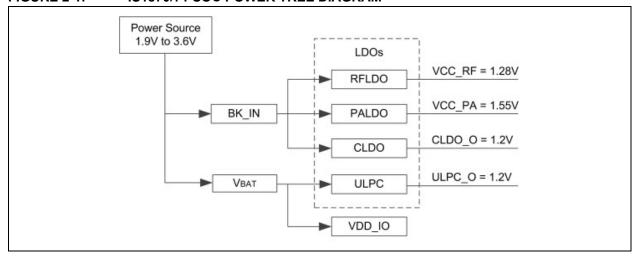

#### 2.1.1 PMU

The IS1870/71 SoC includes a DC-DC converter and four LDOs. Microchip's Bluetooth Low Energy software stack is used for controlling and operating these LDOs

in various modes, controlling the amount of time the peak current is active, maximizing the battery life. The factory firmware enables the designer to perform the calibration for the internal LDOs to compensate for variations in the board design and other manufacturing-related artifacts.

Figure 2-1 illustrates the power tree diagram of the IS1870/71 SoC.

FIGURE 2-1: IS1870/71 SOC POWER TREE DIAGRAM

#### 2.1.2 ALWAYS ON LOGIC

Always On (AON) is the hardware-based state machine, which is controlled by Microchip's Bluetooth stack. Together, the software and hardware logic maintain the power-up, power-down and low power sequences of the IS1870/71 SoC, by providing optimal device performance. It includes an RTC timer and I/O detector to wake-up the system from Power-Saving mode using time out or external general I/O transition. This allows the SoC to run in Power-Saving mode while maintaining an active connection with a peer device and minimizing power consumption.

#### 2.1.3 RF

This SoC is controlled by Microchip's Bluetooth stack, which contains an on-chip RF circuit, a controller and a modulator (Tx)/demodulator (Rx). The Tx is used to control the synthesizer's phase and output power and modulate the data based on the Bluetooth Low Energy specifications. The Rx is used to decode the Bluetooth signal and optimize the performance, such as IQ-imbalance, suppress DC and flick noise. It is also used to compensate the frequency drift and offset, and filter out interference to maximize receiver sensitivity.

#### 2.1.4 MCU

Microchip provides the Bluetooth Low Energy software stack, which runs on the IS1870/71 SoC's internal 8051 core. The stack resides in a combination of ROM, RAM and embedded Flash. The software stack is responsible for scheduling the Bluetooth Low Energy tasks and for processing the Bluetooth Low Energy protocol and profiles.

#### 2.2 System Block Specification

The following are the system block specifications.

Note:

The system blocks which make up the IS1870/71 SoC are listed below. However, some of the blocks used in the IS1870/71 SoC are controlled by the default factory firmware and are not available to the designer.

#### 2.2.1 RF

- · Bluetooth BT5.0 LE compliant SoC

- Frequency: 2.402 GHz to 2.480 GHz

- Programmable transmit output power up to +3 dBm maximum

- -25 dBm minimum Tx power to search nearby devices

- -90 dBm typical receiver power sensitivity

- · Digital RSSI indicator (-50 dBm to -90 dBm)

- -40°C to +85°C Bluetooth Low Energy RF certified

#### 2.2.2 PMU

- Operating battery input voltage range: 1.9V to 3.6V

- 1.28V RFLDO: RF IP power supply

- 1.55V PALDO: RF Tx power amplify supply

- 1.2V CLDO: Core-logic and memories supply

- · 1.55V DC-DC switching buck converter

- 1.2V programmable ULPC to supply AON-logic and retention memory

- AON-logic to control power-up, power-down and wake-up procedures

- Internal 32 kHz (±250 ppm) ultra-low power oscillator

- · Power-on Reset

#### 2.2.3 MCU

- 8051 core with scalable clock

- ROM: 32 KB

- · Main SRAM: 24 KB

- Embedded Flash: 256 KB for Device Firmware Upgrade (DFU) and run-time data storage

Note:

The Microchip provided Bluetooth Low Energy stack uses a portion of the available memory listed above. With the default factory firmware, the amount of memory used is fixed and the free memory is not available to the designer. As it is expected, the application will reside in the external host MCU. For details on altering the default factory setup, please contact your local Microchip representative.

#### 2.2.4 PERIPHERALS

- · Flexible GPIO pin configuration

- · ADC:

- 0V to 3.6V, 12-bit SDM-ADC with 16-channel (IS1870) or 6-Channel (IS1871) hybrid-I/O (Multi-Function). It can be configured as ADC or GPIO input

- Internal 1.9V to 3.6V battery voltage monitor

- Precision Temperature Sensor (PTS) for ambient temperature detection

- 4 MHz clock-rate full duplex 4-wire SPI with 256 bytes buffer DMA

- HCI over UART up to 921600 bps with flow-control

- Two wire serial interface (compatible to I<sup>2</sup>C)

**Note:** This peripheral is not available with the default factory firmware. For details on altering this default factory setup, contact your local Microchip representative.

Three wire serial interface (compatible to SPI)

Note: This peripheral is not available with the default factory firmware. For details on altering this default factory setup, please contact your local Microchip representative.

- GPIO pins with input internal pull up /Hi-Z selectable

- 24-bit low-power Real Time Counter (RTC) for background timer in Standby mode

- Watchdog timer

- Event Counter option (P1\_4 and P1\_5) provides capture/counter function to external events for frequency calculation. It provides 1K/32K/1M/16M clock rate option to count the frequency range from 60 Hz to 1 MHz. The continuous/one shot count mode can be selected

- Specific GPIO pins (P1\_6 and P1\_7) support external 32.768 kHz crystal option for RTC; however, the default from the factory is set to use the internal 32 kHz ultra low-power oscillator

- · PWM:

- 16-bit PWM design

- Four Individual frequency and individual duty cycle channel outputs multiplexed with GPIO pins (P2\_1, P2\_2, P2\_3 and P2\_5)

- Three clock source (32K, 1M and 16M) selections to program frequency range from 0.488 Hz to 8 MHz

- Double buffers output compare registers and top register to avoid glitch

- Two pair output configurable as inverse channel

#### 2.3 Host MCU Interface Over UART

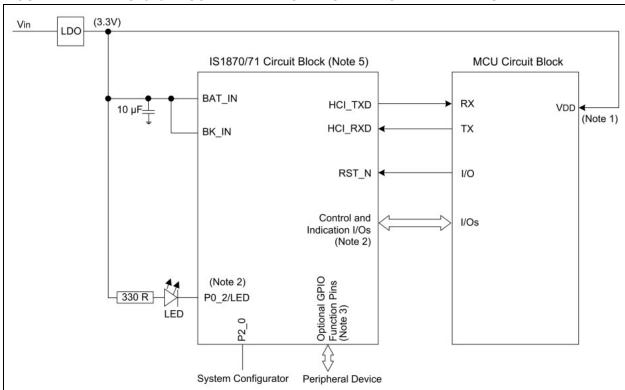

Figure 2-2 illustrates IS1870/71 SoC application block diagram. In the diagram the power supply (3.3V), UART interface and GPIO control and indication are listed.

FIGURE 2-2: IS1870/71 SOC APPLICATION BLOCK DIAGRAM WITH MCU

- Note 1: Ensure BAT IN (I/O voltage) and MCU VDD voltage are compatible.

- **2:** The control and indication ports are configurable in Microchip provided PC tool, referred to as the UI tool, see the product webpage for additional information.

- **3:** Default factory firmware configuration enables the designer to control GPIO functions, ADC, PTS and PWM peripherals. The I<sup>2</sup>C and SPI peripherals are not available with the default firmware. Contact your local Microchip representative for more details.

- **4:** The GPIO applications of the IS1871 SoC have a reduced pin count, and some of the GPIO pins are not supported in the IS1871 SoC.

NOTES:

#### 3.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the IS1870/71 SoC electrical characteristics. Additional information will be provided in future revisions of this document.

Absolute maximum ratings for the IS1870/71 devices are listed below. Exposure to the maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

#### **Absolute Maximum Ratings**

#### (See Note)

| Ambient temperature under bias with parts ending with 102 | 20°C to +70°C        |

|-----------------------------------------------------------|----------------------|

| Ambient temperature under bias with parts ending with 202 | 40°C to +85°C        |

| Storage temperature                                       | 40°C to +125°C       |

| Voltage on VDD with respect to Vss                        | 0.3V to +3.6V        |

| Voltage on any pin with respect to Vss                    | 0.3V to (VDD + 0.3V) |

| Maximum output current sunk by any I/O pin                | 12 mA                |

| Maximum output current sourced by any I/O pin             | 12 mA                |

| ESD (according to machine model, JEDEC EIA/JESD22-A115-C) |                      |

| Maximum output for all pins, excluding RF Tx pin          | ±200V                |

| Maximum output for all pins                               | ±150V                |

| Maximum output (human-body model)                         | ±2 kV                |

| Maximum output (charge-device model)                      | ±150V                |

**Note:** Stresses listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only. The functional operation of the device at those or any other conditions, and those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 3-1 provides the recommended operating conditions of the IS1870/71 SoC.

TABLE 3-1: RECOMMENDED OPERATING CONDITIONS

| Symbol                                                                    | Min.                 | Тур.                                  | Max.                    |  |  |

|---------------------------------------------------------------------------|----------------------|---------------------------------------|-------------------------|--|--|

|                                                                           | PMU                  |                                       |                         |  |  |

| VDD (VBAT, BK_IN, AVDD)                                                   | 1.9V                 | 3.0V                                  | 3.6V                    |  |  |

| RST_N                                                                     | 1.9V                 | 3.0V                                  | 3.6V                    |  |  |

| Other I/O                                                                 | 1.9V                 | _                                     | 3.6V                    |  |  |

|                                                                           | GPIO                 |                                       |                         |  |  |

| Vін (Input High Voltage)                                                  | 0.7 VDD              | _                                     | VDD                     |  |  |

| VIL (Input Low Voltage)                                                   | VSS                  | _                                     | 0.3 VDD                 |  |  |

| Voн (Output High Voltage) (High drive, 12 mA)                             | 0.8 VDD              | _                                     | VDD                     |  |  |

| Vol (Output Low Voltage) (High drive, 12 mA)                              | VSS                  | _                                     | 0.2 VDD                 |  |  |

| Pull up Resistance                                                        | 34 kOhm              | 48 kOhm                               | 74 kOhm                 |  |  |

| Pull down Resistance                                                      | 29 kOhm              | 47 kOhm                               | 86 kOhm                 |  |  |

| Sup                                                                       | ply Current (see Not | e 1)                                  |                         |  |  |

| Tx mode peak current at VDD=3V,<br>Tx=0 dBm, Buck mode                    | _                    | 10 mA at +25°C                        | 13 mA at<br>+70°C/+85°C |  |  |

| Rx mode peak current at VDD=3V, Buck mode                                 | _                    | 10 mA at +25°C                        | 13 mA at<br>+70°C/+85°C |  |  |

| "Reduced current consumption" low power mode current (see <b>Note 2</b> ) | _                    | 60 μA at +25°C                        | _                       |  |  |

| "Shutdown" low power mode current (see Note 2)                            | 1.0 µA               | _                                     | 2.9 μΑ                  |  |  |

| Analog-to-Digit                                                           | al Converter (ADC) f | or IS1870/71-202                      |                         |  |  |

| Full scale (BAT_IN)                                                       | 0V                   | 3.0V                                  | 3.6V                    |  |  |

| Full scale (AD0 to AD15)                                                  | 0V                   | _                                     | 3.6V                    |  |  |

| Operating Temperature Range                                               | -40°C                | 25°C                                  | 85°C                    |  |  |

| Operating current                                                         | _                    | _                                     | 500 μΑ                  |  |  |

| DNL (ENOB 10-bit, ADC in 32 KHz Mode) (see Note 3 and 4)                  | -1                   | _                                     | +1.5                    |  |  |

| INL (ENOB 10-bit, ADC in 32 KHz Mode) (see Note 3 and 4)                  | -2 LSB               | _                                     | +2 LSB                  |  |  |

| Precise Temperature Sensor (PTS) for IS1870/71-202                        |                      |                                       |                         |  |  |

| Detect range                                                              | -40°C                | _                                     | +85°C                   |  |  |

| Digital Output                                                            | 1160                 | _                                     | 2649                    |  |  |

| Resolution                                                                | _                    | 12-bit/°C                             | _                       |  |  |

| Accuracy                                                                  | -3°C                 | — — — — — — — — — — — — — — — — — — — | +3°C                    |  |  |

- **Note 1:** The current measurements are characterized across a sample of the BM70/71 module at room temperature (+25°C), unless otherwise noted.

- 2: For more details on "Reduced current consumption" or "Shutdown" low power modes, refer to the "BM70/71 Bluetooth® Low Energy Module User's Guide" (DS50002542). This rating is part of the characterization of the default factory firmware.

- **3:** ADC performance characterized with V1.06 production firmware across a set of IC's are not tested during production.

- 4: Calculated DNL/INL values are determined using "Best Fit" method.

Table 3-2 provides the RF specifications of the IS1870/71 SoC.

TABLE 3-2: RF SPECIFICATIONS

| Parameter                                                            |                        | Min.     | Тур.       | Max.     |

|----------------------------------------------------------------------|------------------------|----------|------------|----------|

|                                                                      |                        | Trans    | mitter     |          |

| Frequency                                                            |                        | 2402 MHz | _          | 2480 MHz |

| Output Power                                                         |                        | _        | 0 dBm      | _        |

| RF Power Control Ra                                                  | ange                   | -25 dBm  | _          | 3 dBm    |

| In-band Spurious (N±                                                 | :2)                    | _        | -38.5 dBm  | _        |

| In-band Spurious (N±                                                 | :3)                    | _        | -43.25 dBm | _        |

| Modulation Characteristic - Frequency Deviation (see <b>Note 1</b> ) |                        | _        | 247 kHz —  |          |

|                                                                      |                        | Reco     | eiver      |          |

| Frequency                                                            |                        | 2402 MHz | _          | 2480 MHz |

| Sensitivity Level (Inte                                              | erference active)      | _        | -90 dBm    | _        |

| Interference Perfor-                                                 | Co-channel             | _        | 17 dB      | _        |

| mance                                                                | Adjacent<br>± 1 MHz    | _        | 0 dB       | _        |

|                                                                      | Adjacent<br>± 2 MHz    | _        | -25 dB     | _        |

|                                                                      | Adjacent >=<br>± 3 MHz | _        | -32 dB     | _        |

| Intermodulation Char                                                 | acteristic (n=3,4,5)   | _        | -37.5 dBm  | _        |

| Maximum Usable Lev                                                   | vel                    |          | 0 dBm      |          |

**Note 1:** Tested with a known pattern of '00001111'b being transmitted.

## 3.1 Current Consumption Details

## 3.1.1 Tx/Rx CURRENT CONSUMPTION DETAILS

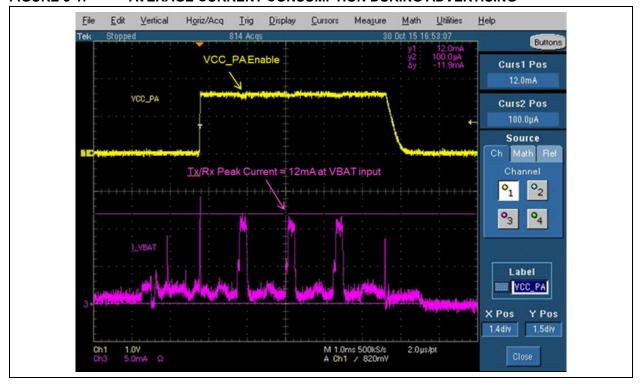

Figure 3-1 illustrates the average current consumption of an advertising event during Bluetooth Low Energy operation of the IS1870/71 SoC.

The peak current of the VBAT input is 12 mA and the average current is around 230  $\mu$ A. In this example the advertising interval is 100 ms and current consumption is measured at 3.3V VBAT input.

FIGURE 3-1: AVERAGE CURRENT CONSUMPTION DURING ADVERTISING

## 4.0 PACKAGE INFORMATION

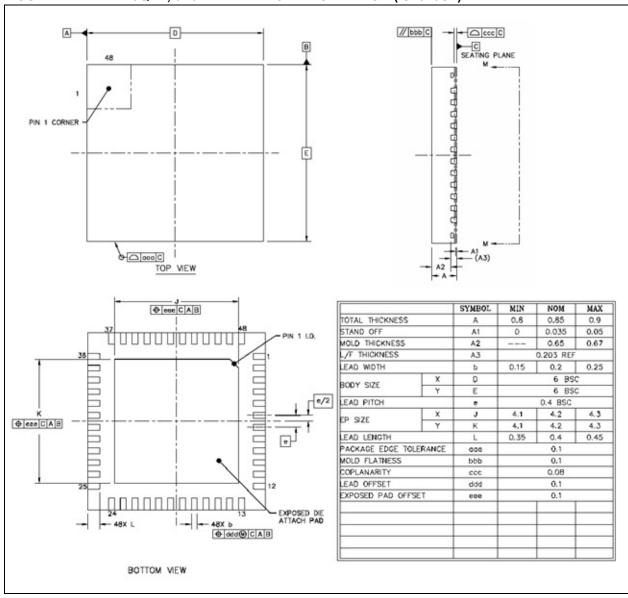

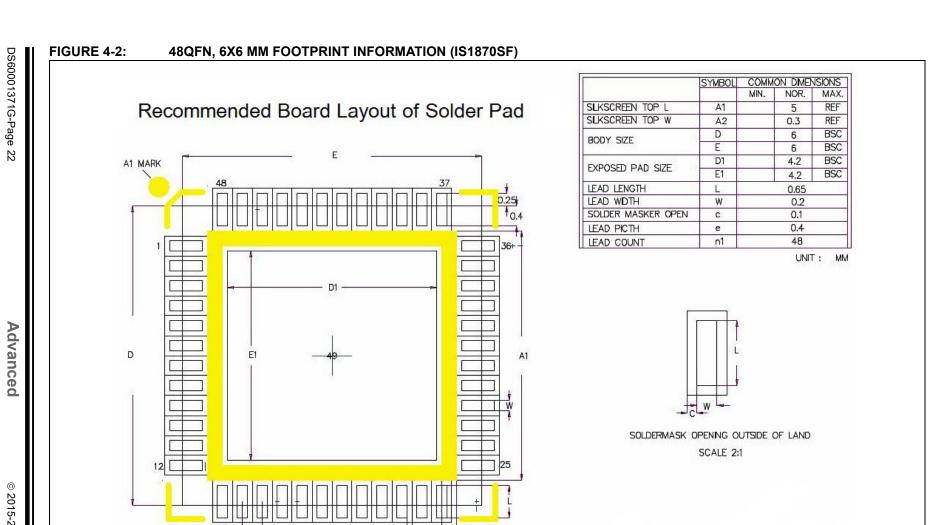

Figure 4-1 through Figure 4-5 illustrate the package marking information of the IS1870SF IC.

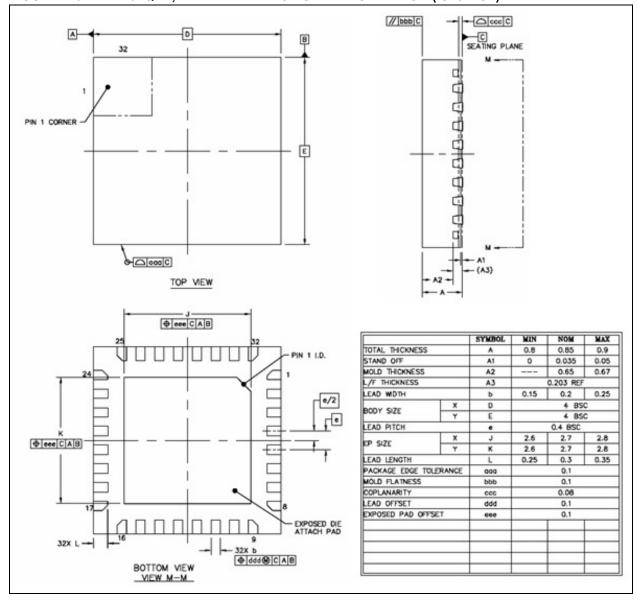

## 4.1 48QFN, 6x6 mm SoC Outline (IS1870SF)

FIGURE 4-1: 48QFN, 6X6 MM PACKAGE INFORMATION (IS1870SF)

TOP VIEW

## 4.2 32QFN, 4x4 mm SoC Outline (IS1871SF)

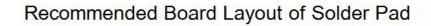

FIGURE 4-3: 32QFN, 4X4 MM PACKAGE SIZE INFORMATION (IS1871SF)

DS60001371G-Page 24

FIGURE 4-4: 32QFN FOOTPRINT INFORMATION (IS1871SF)

|                    | SYMBOL | COMM | ON DME | SIONS |

|--------------------|--------|------|--------|-------|

|                    | DY 63  | MIN. | NOR.   | MAX.  |

| SLKSCREEN TOP L    | A1     |      | 3.3    | REF   |

| SLKSCREEN TOP W    | A2     |      | 0.2    | REF   |

| BODY SIZE          | D      |      | 4      | BSC   |

| BOD I SIZE         | E      |      | 4      | BSC   |

| EXPOSED PAD SIZE   | D1     |      | 2.7    | BSC   |

| EXPOSED PAU SIZE   | E1     |      | 2.7    | BSC   |

| LEAD LENGTH        | L      |      | 0.5    |       |

| LEAD WIDTH         | W      | =    | 0.2    |       |

| SOLDER MASKER OPEN | С      | 0.1  |        |       |

| LEAD PICTH         | е      | 0.4  |        |       |

| LEAD COUNT         | n1     |      | 32     |       |

UNIT: MM

SOLDERMASK OPENING OUTSIDE OF LAND SCALE 2:1

#### FIGURE 4-5: PACKAGE MARKING INFORMATION

48-Lead QFN (6x6x0.9 mm)

O iSSC

XXXXXXXXXX

XXXXXXXXXX

YYWWNNN

ISSC

IS1870SF

102 (3)

1527B9S

32-Lead QFN (4x4x0.9 mm)

issc xxxxxxxxxx xxxxxxxxxx yywwnnn

O **iSSC**IS1871SF

102 (**93**)

1525Q0P

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

\* This package is Pb-free. The Pb-free JEDEC designator (@3)

Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

can be found on the outer packaging for this package.

NOTES:

## 5.0 REFLOW PROFILE AND STORAGE CONDITION

Figure 5-1 and Figure 5-2 illustrate the reflow profiles and stencil information of the IS1870/71 SoC.

## 5.1 Stencil of SMT Assembly Suggestion

#### 5.1.1 STENCIL TYPE AND THICKNESS

- · Laser cutting

- · Stainless steel

- Thickness: 0.5 mm pitch, thickness more than 0.15 mm

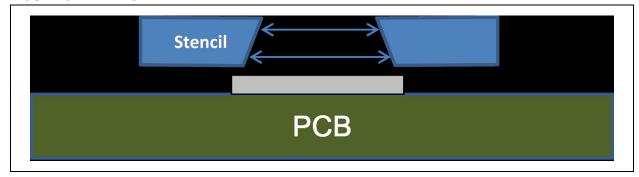

## 5.1.2 APERTURE SIZE AND SHAPE FOR TERMINAL PAD

- · Aspect ratio (width/thickness) more than 1.5

- · Aperture shape

- The stencil aperture is designed to match the

- pad size on the PCB

- Oval-shape opening is used to get the optimum paste release

- Rounded corners to minimize the clogging

- Positive taper walls (5° tapering) with the bottom opening larger than the top opening

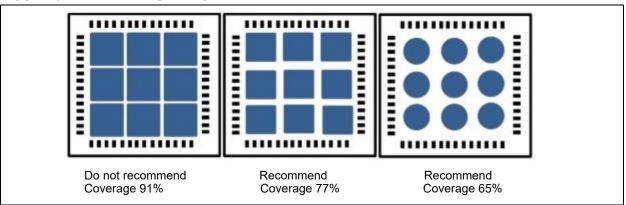

## 5.1.3 APERTURE DESIGN FOR THERMAL PAD

- Small multiple openings are used instead of one big opening, see Figure 5-1

- 60 to 80% solder paste coverage

- · Rounded corners to minimize clogging

- Positive taper walls (5° tapering) with the bottom opening larger than the top opening, see Figure 5-2

#### FIGURE 5-1: REFLOW PROFILE

#### FIGURE 5-2: STENCIL TYPE

#### 5.2 Reflow Profile

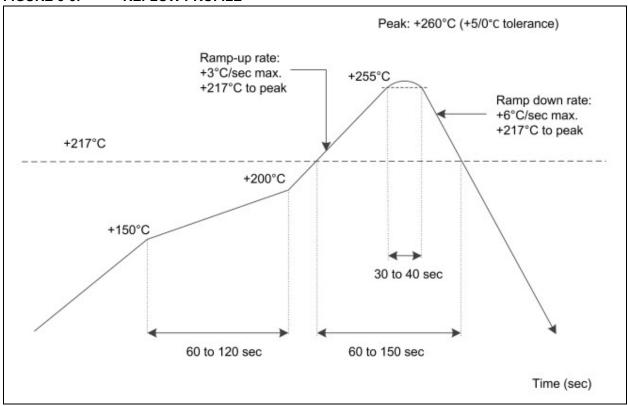

Figure 5-3 illustrates the reflow profile and the following are its specific features:

- Standard Condition: IPC/JEDEC J-STD-020

- Preheat: +150 °C to +200 °C for 60 to 120 seconds

- Average ramp-up rate (+217°C to peak): +3°C/sec

- Temperature maintained above +217 °C : 60 to 150 seconds

- Time within +5 °C of peak temperature: 30 to 40 seconds

- Peak temperature: +260 °C with 5/-0 °C tolerance

- Ramp-down rate (peak to +217°C): +6°C/sec. max

- Time within +25°C to peak temperature: 8 minutes max

- · Cycle interval: 5 minutes

FIGURE 5-3: REFLOW PROFILE

## 5.3 Storage Condition

Users are required to follow these specific storage conditions for the IS1870/71 SoC.

- The calculated shelf life in the sealed bag is 24 months at <+40 °C and <90% Relative Humidity (RH)

- After the bag is opened, devices that are subjected to reflow solder or other high temperature process must be mounted within 168 hours of factory conditions, i.e <+30 °C /60% RH</li>

NOTES:

## 6.0 ORDERING GUIDE

Table 6-1 provides the ordering information for the  $IS1870/71\ SoC.$

TABLE 6-1: ORDERING GUIDE

| Device       | Bluetooth Version                                                  | Operating<br>Temperature Range | Package                                                | Part No.     |

|--------------|--------------------------------------------------------------------|--------------------------------|--------------------------------------------------------|--------------|

| IS1870SF-102 | Bluetooth Low Energy<br>SoC, Bluetooth Low<br>Energy 5.0 compliant | -20°C to +70°C                 | 48-Lead QFN, 6x6x0.9 mm <sup>3</sup> ,<br>0.4 mm pitch | IS1870SF-102 |

| IS1871SF-102 | Bluetooth Low Energy<br>SoC, Bluetooth Low<br>Energy 5.0 compliant | -20°C to +70°C                 | 32-Lead QFN, 4x4x0.9 mm <sup>3</sup> ,<br>0.4 mm pitch | IS1871SF-102 |

| IS1870SF-202 | Bluetooth Low Energy<br>SoC, Bluetooth Low<br>Energy 5.0 compliant | -40°C to +85°C                 | 48-Lead QFN, 6x6x0.9 mm <sup>3</sup> ,<br>0.4 mm pitch | IS1870SF-202 |

| IS1871SF-202 | Bluetooth Low Energy<br>SoC, Bluetooth Low<br>Energy 5.0 compliant | -40°C to +85°C                 | 32-Lead QFN, 4x4x0.9 mm <sup>3</sup> ,<br>0.4 mm pitch | IS1871SF-202 |

**Note:** The IS1870/71 SoC can be purchased through a Microchip representative.

Visit http://www.microchip.com/ for ordering information.

NOTES:

#### APPENDIX A: REFERENCE CIRCUIT

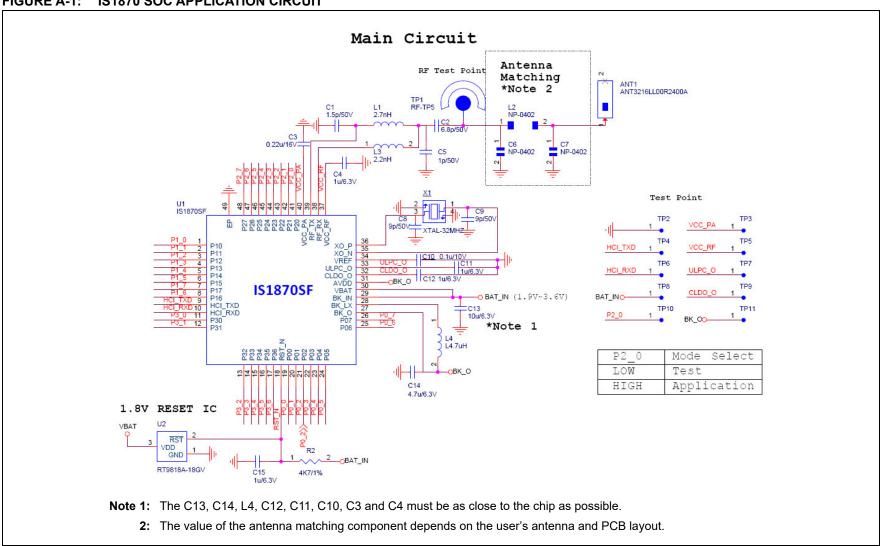

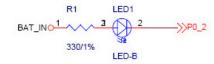

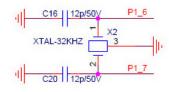

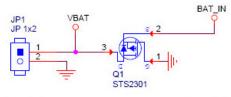

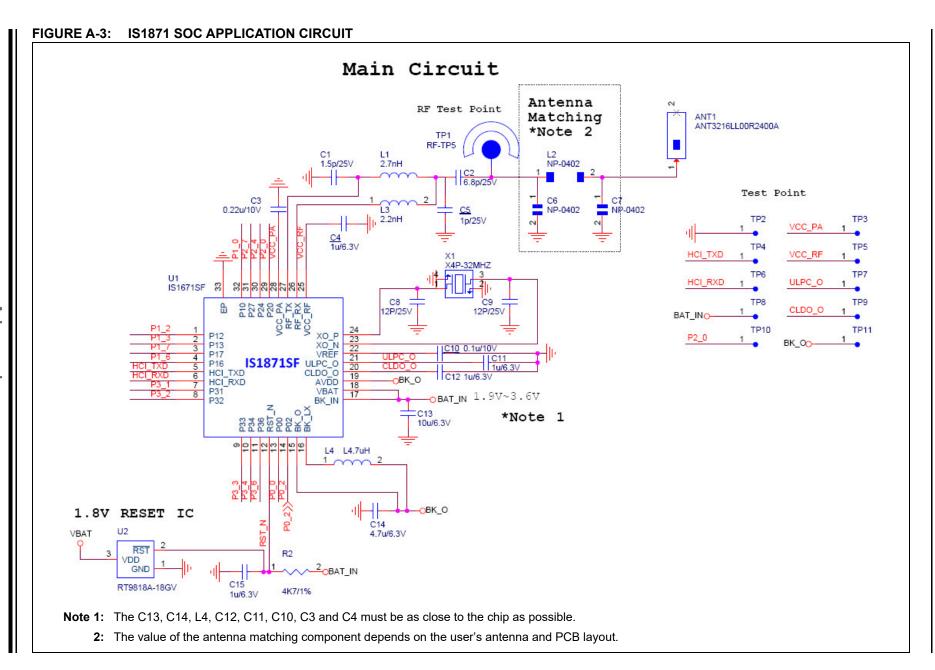

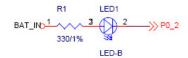

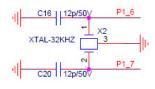

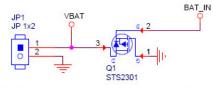

Figure A-1 through Figure A-4 illustrate a typical application circuit of the IS1870 and IS1871 SoC.

The application circuit lists the RF matching circuit, PMU power tree, LED option, test points and configuration table. The GPIOs can be configured to general I/O functions or the function of ADC, PTS, PWM and external 32.768 kHz crystal.

#### FIGURE A-1: IS1870 SOC APPLICATION CIRCUIT

DS60001371G-Page 34

FIGURE A-2: IS1870 SOC APPLICATION CIRCUIT (OPTIONAL)

## Optional Circuit

## LED Option

\*Used in BAT\_IN>3.0V condition to ensure LED is bright enough

## External 32KHz Crystal Option

## Battery Reverse Protection

\*Voltage reverse protection in reverse battery input condition

IS1870/71

DS60001371G-Page 36

FIGURE A-4: IS1871 SOC APPLICATION CIRCUIT (OPTIONAL)

## Optional Circuit

## LED Option

\*Used in BAT\_IN>3.0V condition to ensure LED is bright enough

## External 32KHz Crystal Option

## Battery Reverse Protection

\*Voltage reverse protection in reverse battery input condition

## APPENDIX B: LAYOUT GUIDELINES

## **B.1** RF Matching

The RF traces (Tx, Rx and antenna path) on the PCB antenna must match the 50 Ohm impedance. In Figure A-1, value of L1, L3, C1, C2 and C5 are fixed. The antenna matching components, C6, C7 and L2, must be adjusted to match with the 50 Ohm 2.4 GHz antenna.

#### B.2 PMU

The PMU section components, such as V<sub>BAT</sub>, BK\_IN, BK\_O, BK\_LX, AV<sub>DD</sub>, ULPC\_O, CLDO\_O, VREF must be kept close to the IS1870/71 SoC. The L4 and C14 of Buck section, illustrated in Figure A-1, must be selected carefully. The capacitor C14 is either 4.7  $\mu\text{F}/6.3\text{V}$ , X5R or X7R type. The inductor L4 must be a high current (lpc>300 mA) and low DCR (<1 Ohm) type.

For additional information on the PCB antenna design guidelines, contact your local Microchip sales office. A list of Microchip sales offices is given on the back page of this document.

## **B.3** Crystal

The XI 32 MHz crystal specification must be within the  $\pm 10$  ppm range, see Figure A-1.

NOTES:

### APPENDIX C: REVISION HISTORY

## **Revision A (October 2015)**

This is the initial released version of this document.

## **Revision B (October 2015)**

This revision includes the following changes as well as minor updates to text and formatting, which were incorporated throughout the document.

| Status                | Description                                          |

|-----------------------|------------------------------------------------------|

| "Features"            | The section has been updated with new information.   |

| "Packages"            | The section is updated with the package information. |

| 1.0 "Device Overview" | Updated Figure 1-1 and Figure 1-2.                   |

|                       | Added Table 1-1                                      |

## Revision C (March 2016)

This revision includes the following changes and minor updates to text and formatting, which were incorporated throughout the document.

| Status                           | Description                                                                                                            |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| "Features"                       | The section is updated with new information.                                                                           |  |

| 1.0 "Device Overview"            | Updated Figure 1-1 and Figure 1-2. Updated Table 1-1 and Table 1-2.                                                    |  |

| 2.0 "System Block Details"       | Updated 2.2 "System Block Specification" and 2.3 "Host MCU Interface Over UART" with new information.                  |  |

| 3.0 "Electrical Characteristics" | Updated 3.1.1 "Tx/Rx Current Consumption Details". Updated Figure 3-1 and Figure 3-1. Updated Table 3-1 and Table 3-2. |  |

| 5.3 "Storage Condition"          | Deleted Figure 5-4.                                                                                                    |  |

| 6.0 "Ordering Guide"             | Updated Table 6-1                                                                                                      |  |

| Appendix A: "Reference Circuit"  | Updated Figure A-1 and Figure A-3<br>Added Figure A-2 and Figure A-4                                                   |  |

| Appendix C: Bill of Material     | Deleted                                                                                                                |  |

## **Revision D (February 2017)**

This revision includes the following changes and minor updates to text and formatting, which were incorporated throughout the document.

| Section                          | Update Description                                                                                     |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------|--|

| "Features"                       | Updated this section.                                                                                  |  |

| "Packages"                       | Updated the I/O pins details.                                                                          |  |

| "Operating Conditions"           | Updated the operating temperature details.                                                             |  |

| 1.0 "Device Overview"            | Updated Figure 1-1 and Figure 1-2.                                                                     |  |

| 2.0 "System Block Details"       | Updated Figure 2-2.                                                                                    |  |

| 3.0 "Electrical Characteristics" | Updated ambient temperature, maximum output (human-body model) details and Table 3-1. Added Table 3-2. |  |

| 6.0 "Ordering Guide"             | Updated Table 6-1                                                                                      |  |

## Revision E (February 2018)

This revision includes the following changes and minor updates to text and formatting, which were incorporated throughout the document.

| Section                          | Update Description |

|----------------------------------|--------------------|

| 1.0 "Device Overview"            | Updated Table 1-2. |

| 3.0 "Electrical Characteristics" | Updated Table 3-1. |

## **Revision F (February 2021)**

This revision includes the following changes and minor updates to text and formatting, which were incorporated throughout the document.

| Section                          | Update Description                                                   |

|----------------------------------|----------------------------------------------------------------------|

| 2.2 "System Block Specification" | Performed following change:  • 4-wire master/slave SPI to 4-wire SPI |

| 3.0 "Electrical Characteristics" | Updated the following values in Table 3-1.                           |

|                                  | Digital Output Min value from 1387 to 1160                           |

|                                  | Digital Output Max value from 2448 to 2649                           |

## **Revision G (September 2021)**

This revision includes the following changes and minor updates to text and formatting, which were incorporated throughout the document.

| Section                          | Update Description                                                       |  |

|----------------------------------|--------------------------------------------------------------------------|--|

| 1.0 "Device Overview"            | Performed following change:  • Updated Bluetooth version from 4.2 to 5.0 |  |

|                                  | Updated Table 1-2 with new terminology, see the following note           |  |

| 2.2 "System Block Specification" | Performed the following change:                                          |  |

|                                  | Updated Bluetooth version from 4.2 to 5.0                                |  |

| 6.0 "Ordering Guide"             | Performed the following change:                                          |  |

|                                  | Updated Bluetooth version from 4.2 to 5.0                                |  |

Note:

Microchip is aware that some terminologies used in the technical documents and existing software codes of this product are outdated and unsuitable. This document may use these new terminologies, which may or may not reflect on the source codes, software GUIs, and the documents referenced within this document. The following table shows the relevant terminology changes made in this document.

#### TABLE G-1: TERMINOLOGY RELATED CHANGES

| Old Terminology | New Terminology | Description                                |

|-----------------|-----------------|--------------------------------------------|

| Master mode     | Central mode    | Table 1-2 is updated with new terminology. |

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">https://www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, Symmcom, and Trusted Time are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015-2021, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-5224-8899-6

## Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423

Fax: 972-818-2924 **Detroit**

Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323

Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

**China - Chengdu** Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu

Tel: 82-53-744-4301 **Korea - Seoul** Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4485-5910 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

**Germany - Karlsruhe** Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820